Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

Selected Reading

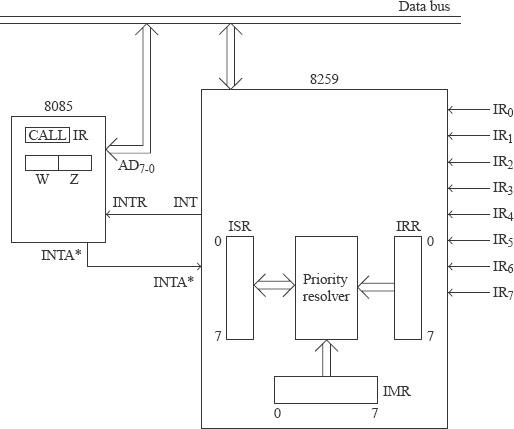

Interrupt mask register in 8259

It stores the levels of interrupts to be masked by means of storing the bits of the interrupt level already masked. It differs from other registers by means of only masking of the bits. Other processes remained intact. Let’s take for the assumption that the requests to the IR4 AND IR6 should not be an interrupt to the processor which can be well achieved by setting the bits of IMR to 1. The IMR is written by OCW1 command. The processor here also has the capability to read the contents of the IMRregister. To complete this task, the processor has to read the high port of 8259.

Fig:8259 interfaced along with 8085 processor

Advertisements