Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

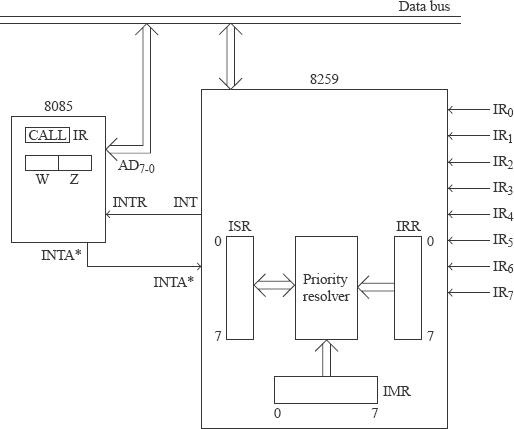

Architecture of 8259

8259 Microprocessor is architected in a unique style. It can program by means of some interrupts conditions by means of level or interrupt level often called edge-triggered interrupt level. Masking is done to individual interrupt bits. As the number of 8259 increases interrupt pins up to 64 can be obtained. There are 3 registers 8259 contains along with one priority resolver(PR). They are as follows −

Interrupt Request Register(IIR) − It stores the bits who requests the interrupt.

Interrupt service register(ISR) − It stores the currently interrupt levels.

Interrupt Mask Register(IMR) − Stores the interrupt levels to be masked.

PriorityResolver(PR) − Set the priority of interrupts by examining all the three registers and set the interrupt level inISR having the highest priority.

SP/EN (low active pin) − When its value is 1 it works in master mode and when its value is 0 it works in slave mode.

Cascade Buffer − Used for cascading more Programmable Interrupt Controller.

Fig −8259 interfaced along with 8085 processor