Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

In-service register in 8259

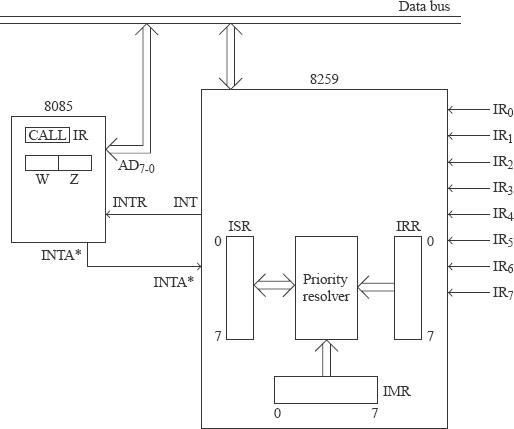

Also, an 8-bit register which keeps track records of the interrupt requests that are currently being executed. If the request IR6 is currently being served, whose contents of ISR will be 01000000. If by any means the request to IR3 becomes active during the service process of IR6, 8259 sets bit 3 of ISR to 1 and activates the output INT. But bit 6 of ISR always remains set at 1 asIR6 request which is not fully serviced. Hence the contents ofISR become 01001000. The following assumptions stated below helps this to happen.

Until 8259 operates in a complete nested mode, without the priority of rotating such that IR3 gets high priority than IR6.

The processor should enable interrupts in the routine specified for IR6.

Till the IR3 request has not been masked.

Fig:8259 interfaced along with 8085 processor