Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Trap interrupt pin in 8085

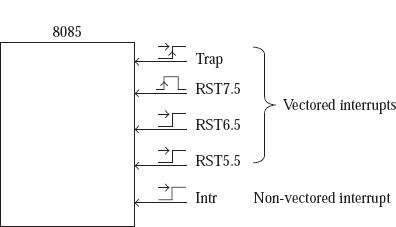

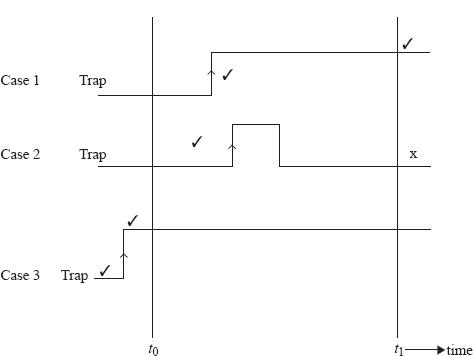

A non-maskable interrupt is a Trap Interrupt which implies that whenever this pin gets activated, the 8085 always gets interrupted even if the state of 8085 is in DI. The input of Trap input is level sensitive and edge sensitive. Hence the Trap line always makes a transition from 0 to 1, and remains in state 1 until the end of the execution of an instruction for the interruption of 8085.

A vectored-interrupt in 8085 is a TRAP. The starting address of 8085 is known by itself the of the ISS as 4.5 * 8 = 0024H. Hence we name the TRAP pin equivalently as RST 4.5. It is referred as trap by INTEL. Non-maskable interrupt is TRAP whereas maskable is interrupt. At location 4.5 * 8, we do not have the ISS. As an example, in the ALS kit we have instruction JMP 0182H in the 3 bytes starting at 4.5 * 8 = 0024H.