Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is speculative execution in computer architecture?

A processor extends to execute instructions speculatively until the condition is resolved. The time interval between the beginning of the conditional execution and the resolution of the equivalent condition can change significantly. The condition is resolved the immediately following cycle.

This appears when the specified condition defines the result of a simple operation, including integer addition, subtraction, or logical operation. In the case of long operations, including FX or FP division, multiple cycles will pass earlier the condition can be resolved.

The superscalar processor can issue several instructions in each cycle. Thus, during speculative execution scores of instructions are executed before the specified condition becomes evaluable.

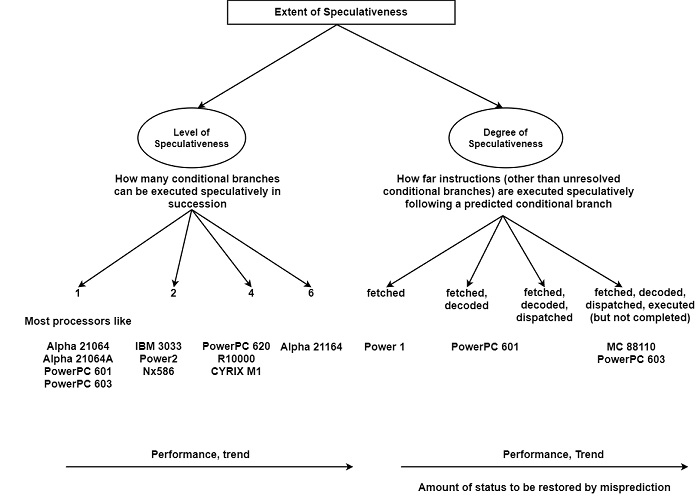

There are two main aspects such as the level and the degree of speculativeness as shown in the figure. By the level of speculativeness, it can understand the multiple conditional branches that can be executed speculatively in sequence. It is beneficial for performance if a second, third, and so on, the unresolved conditional branch does not terminate speculative execution. This requirement is even more compulsory for a superscalar processor adequate to issuing multiple instructions per cycle.

The Power2 allows two, the PowerPC 620 and R10000 four and the α 21164 as many as six pending conditional branches. The processors that allow only one pending conditional branch resemble a basic block scheduler, which schedules instruction for parallel execution up to the end of the current basic block, while processors that permit multiple pending conditional branches are similar to global schedulers, going beyond basic block boundaries.

The second method is the degree of speculativeness. This concept associates with how far instructions, other than unresolved conditional branches, are implemented following a guessed conditional branch. Here, processors pursue different schemes as shown in the figure. In the simplest case, speculative execution goes no further than fetching some instructions belonging to the predicated path, such as the Power1.

A higher degree of speculativeness is found when instruction along the predicated path is fetched and decoded, or fetched, decoded, and dispatched as in the PowerPC 601. Processors with even a high degree of speculativeness fetch, decode, dispatch, and execute instructions after a pending conditional branch, although without completing them, as in the MC 88110 or PowerPC 603.

For instance, the MC 88110 allows instructions to be executed speculatively and provides a mechanism to undo them in the case of a misprediction. This mechanism aims at retaining sequential consistency for out-of-order execution. It is based on a history buffer and can undo two instructions per cycle.