Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is Latches in Computer Architecture?

A latch is a device with particularly two stable states and these states are high-output and low-output. A latch has a feedback direction, to maintain the data. Latches can be memory devices and can save one bit of information. It is used to “latch onto” data and save it in the required area. One of the most generally used latches is the SR latch.

SR Latch

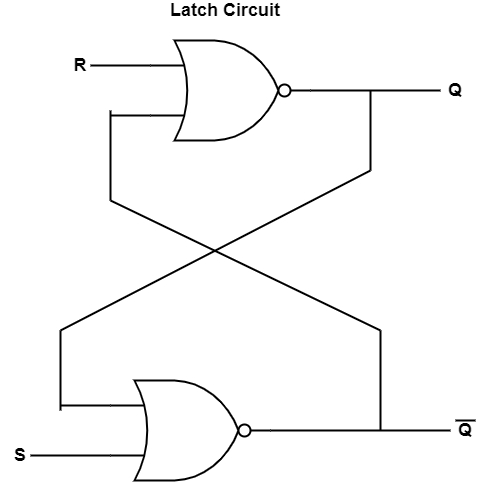

An SR latch is an asynchronous device. An SR latch does not rely upon control signals but relies only on the state of the S and R inputs. An SR latch can be generated by interlinking two NOR gates with a cross-feedback loop. SR latches can also be constructed by interlinking NAND gates but the inputs are exchanged and contradict.

A simple SR latch circuit is demonstrated in the diagram, where the inputs S and R define ’set’ and ’reset’. The present output of a latch is based on the state of the latch. Therefore, the output at nth instant defined as Qn is based on output at (n−1)th instant defined by Qn-1.

The table demonstrates the truth table for the SR latch.

| S | R | Qn | $\overline{Q_{n}}$ |

|---|---|---|---|

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 |

| 0 | 0 | Qn-1 | $\overline{Q_{n}-1}$ |

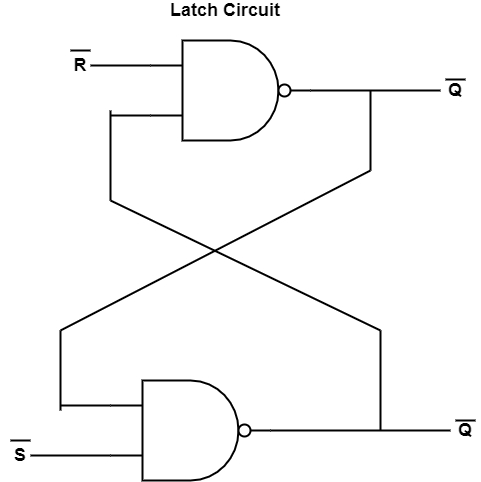

A similar SR latch can be constructed using NAND gates. The diagram shows how an SR latch can be generated using the NAND gate.

The table demonstrates the truth table for an SR latch that is generated using a NAND gate.

| $\overline{S}$ | $\overline{R}$ | Qn | $\overline{Q_{n}}$ |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 1 | 1 | Qn-1 | $\overline{Q_{n}-1}$ |