- Computer - Home

- Computer - Overview

- Computer - Advantages & Disadvantages

- Computer - Classification

- Computer - Applications

- Computer - History & Evolution

- Computer - System Characteristics

- Computing Origins

- Computer - Origins

- Computer - Generations

- Computer - Types

- Computer Components

- Computer - Components

- Computer - CPU

- Computer - CPU Components

- Computer - Arithmetic Logic Unit (ALU)

- Computer - Control Unit

- Computer - Input Devices

- Computer - Output Devices

- Computer - Memory Units

- Computer Hardware

- Computer - Hardware

- Computer - Motherboard

- Computer - GPU

- Computer - PSU

- Computer Software

- Computer - Software

- Computer - Software Types

- Computer Data Storage & Memory

- Computer - Data Storage

- Computer - Types of Data Storage

- Computer - Hard Disk Drives (HDD)

- Computer - Solid State Drives (SSD)

- Computer - Memory Cards

- Computer - Optical Storage

- Computer - NAND Flash Memory

- Computer - NVMe Memory

- Computer - CompactFlash Card

- Computer - Cloud Storage

- Computer Memory

- Computer - Memory

- Computer - Primary Memory

- Computer - Secondary Memory

- Computer - RAM

- Computer - ROM

- Computer - DRAM

- Computer - VRAM

- Computer - Cache Memory

- Computer Internet & Intranet

- Computer - Internet and Intranet

- Computer - Internet

- Computer - Extranet

- Computer - Websites

- Computer Office Tools

- Computer - Word Processors

- Computer - Spread Sheet

- Computer - Power Presentations

- Computer - E-mail Tools

- Computer Miscellaneous

- Computer - Ports

- Computer - Number System

- Computer - Number Conversion

- Computer - Data and Information

- Computer - Networking

- Computer - Operating System

- Computer - Keyboard Shortcut Keys

- Computer - Virus

- Computer - Antivirus

- Computer - How to Buy?

- Computer - Available Courses

- Calculator Vs. Computer

- Brain Vs. Computer

- Analog Vs. Digital Computer

- Supercomputer Vs. Mainframe Computer

- Mainframe Vs. Minicomputer

- Printer Vs. Scanner

- OCR Vs. MICR

- File Vs. Folder

- exFAT Vs. FAT32

- FAT32 Vs. NTFS

- FAT32 Vs. exFAT Vs. NTFS

- CPU Vs. GPU

- GUI Vs. CLI

- GUI Vs. CUI

- Cache Memory Vs. Virtual Memory

- Register Vs. Memory

- RAM Vs. CAM

- SRAM Vs. DRAM

- DDR2 Vs. DDR3

- PROM Vs. EPROM

- CD Vs. DVD

- Blu-Ray Vs. DVD

- MMU Vs. MPU

- Computer Terminologies

- Microsoft Windows

- Desktop

- Monitor

- Microphone

- Keyboard

- Keypad

- Mouse

- Printer

- Webcam

- Floppy Disk Drive

- Compact Disc

- Program

- Incognito Mode

- Electronic Mail (E-Mail)

- Server

- Cloud Hosting

- Minicomputers

- Supercomputer

- Bit

- Byte

- Kilobyte

- Megabyte

- Terabyte

- Yottabyte

- Zettabyte

- Exabyte

- Petabyte

- JEDEC

- Hub

- Block Storage

- Username

- URL

- Num Lock

- BIOS

- Bluetooth

- Computer Useful Resources

- Computer - Quick Guide

- Keyboard Function Keys

- Keyboard Shortcuts for Ubuntu

- Computer - Useful Resources

- Computer - Discussion

Computer - Cache Memory

What is Cache Memory?

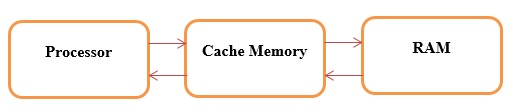

Memory that is smaller and faster than RAM is called cache memory. It is a volatile memory fixed closer to the CPU to provide high-speed data access to the processor and stores frequently used computer programs, applications and data. Generally a cache memory fixes between processor and Random Access Memory.

What does Cache Memory Look Alike?

Cache memory's physical structure can be understood using the below images.

It saves data and instructions that are used a lot so that processing goes faster.

Why Cache Memory is Important?

Cache memory is much faster than main memory, thus the CPU can access data quickly used in execution; cache memory helps to get full utilisation of the CPU. It generally fixes closer to the CPU to communicate with CPU and RAM. Cache memory increases the system's overall performance and efficiency. It reduces the latency that the CPU experiences when retrieving data from main memory.

How does Cache Memory Work?

The data in a cache is typically stored in hardware with immediate access, like RAM. When a user retrieves data, it checks the caching first. If the data is located in the cache, it is called a cache hit. The proportion of attempts that provide a cache hit is known as the cache hit rate or ratio. Data that is not located in the cache is taken from the main memory and put into the cache. This is known as a cache miss. How this is accomplished and what information is expelled from the cache to create space for new data is determined by the caching algorithms, cache mechanisms, and system regulations.

Different caching mechanisms govern the operation of the cache.

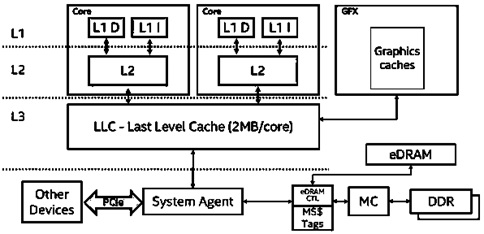

- Cache Hierarchy − Computers normally have L1, L2, and L3 caches are the several layers of cache memory. The L1 cache is the smallest and fastest cache, located closest to the CPU; L2 and L3 caches are larger and slower. Modern processors contain L1, L2, and L3 caches that grow in capacity and latency farther from the CPU cores. Parallel access is achieved by splitting the L1 cache into instruction and data caches.

- Cache Organization − Each block or line of cache memory contains a small bit of data copied from the main memory. The CPU accesses cache memory in fixed-size blocks, not bytes.

- Cache Coherency − Cache coherency ensures cached data matches the main memory data. Cache coherence techniques update other cores' caches when one core writes to a memory location in a multi-core processor.

- Cache Replacement Policies − A cache replacement policy decides which block to evict when the cache is full and a new block is needed. LRU, FIFO, and Random Replacement are common policies.

- Cache Access − The CPU checks the cache before reading or writing data. When data is cached, the CPU can quickly retrieve it. If data is not in the cache (cache miss), the CPU must fetch it from the main memory, which may delay it.

- Cache Management − Optimization of cache utilization maximizes hit rates and minimizes miss penalties. Prefetching, where the processor predicts memory accesses and loads data into the cache, improves cache performance.

Cache memory buffers frequently access data between the CPU and main memory to speed up processing and increase system performance. Modern computer systems require effective management and structure for optimal performance.

Types of Cache Memory

Different types of cache memory, like L1, L2, and L3 cache, have different speeds and amounts of space.

The Levels of Cache Memory: L1, L2, and L3

CPU Cache memory is categorised into three "levels": L1, L2, and L3.

L1 Cache

Level 1 cache is a computer's fastest memory. The CPU's most frequently accessed data resides in the L1 cache. CPU determines L1 cache size. Some high-end consumer CPUs, such as the Intel i9-9980XE, have a 1MB L1 cache, but they are expensive and rare. Server chipsets like Intel's Xeon have 1-2MB L1 memory cache. Before buying, examine the CPU specs to ascertain the L1 cache size. There is no "standard" amount.

The L1 cache normally has two sections: the instruction cache, which stores CPU operation information, and the data cache, which stores operation data.

L2 Cache

Level 2 cache is larger but slower than L1. Modern L2 memory caches are gigabytes, not kilobytes. AMD's top-rated Ryzen 5 5600X has 384KB L1 and 3MB L2 caches and 32MB L3 cache. The L2 cache size depends on the CPU but is usually 256KB to 32MB. Nowadays, most CPUs have more than 256KB L2 cache, which is small. Some of the most powerful current CPUs have L2 memory caches exceeding 8MB. In terms of speed, the L2 cache is slower than the L1 cache but still faster than the system RAM. L2 caches are 25 times faster than RAM, while L1 caches are 100 times faster.

L3 Cache

Level 3 cache. The L3 memory cache was originally on the motherboard. This was long ago when most CPUs were single-core. The L3 cache on top-end consumer CPUs can reach 32MB, while AMD's groundbreaking Ryzen 7 5800X3D CPUs have 96MB. CPU L3 caches in some servers can reach 128MB.

The largest and slowest cache memory unit is L3. Modern CPUs have an on-chip L3 cache. The chip's L1 and L2 caches serve each core, while the L3 cache is more like a memory pool for the whole chip. The following images illustrate the CPU memory cache levels for a 2012 Intel Core i5-3570K CPU and a 2020 AMD Ryzen 5800X CPU. The second image's bottom right corner contains CPU cache data.

Applications of Cache Memory

The primary applications of Cache Memory are as follows −

- Cache stores temporary files; so it is most widely used in the CPU.

- Different programs and software use their cache.

- A web browser has a cache that retains information.

- Caches are utilised by the operating system.

- It stores frequently accessed data which makes data access fast if a user re-accesses it.

Advantages of Cache Memory

Some key advantages of cache memory are as follows −

- Faster Access − It fixes closer to CPU so access data very fast.

- Reducing Memory Latency − It takes very little time to retrieve data from memory which shows it reduces memory latency.

- Increasing effective CPU utilization − It supports full CPU utilisation by fast data accessing and giving it to the CPU so that the execution of instructions or programs is done on time.

- Reduced Power Consumption − Cache memory consumes much less power than other types of storage.

- Scalability − Cache memory can grow with a system's needs.

Overall, a cache memory increases throughput, improves reliability and increases scalability.