Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is Time-shared Common Bus in Computer Architecture?

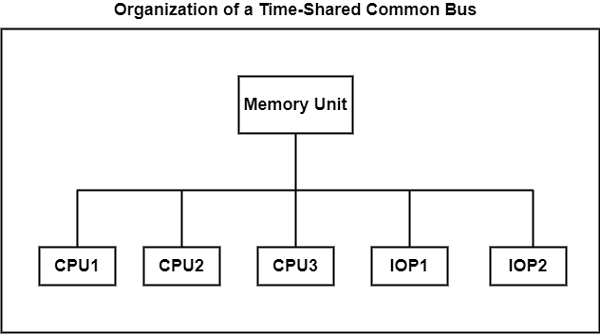

In the time-shared common bus, there are numerous processors linked by a common direction to the memory unit in a common-bus multiprocessor system. The figure shows the organization of time-shared common buses for five processors.

There is only one processor that can interact with the memory of another processor. The processor that is in control of the bus at the time implements transfer operations. Any processor that needs to start a transfer should first check the availability condition of the bus.

During the bus is available, the processor can start a connection with the destination unit to introduce the transfer. A command is issued to advise the destination unit about the task to be implemented. The receiving unit recognizes its address in the bus, and then responds to the control signals from the sender, after which the transfer is initiated.

As all processors share a common bus, the system may display some transfer conflicts. The incorporation of a bus controller that creates priorities among the requesting units helps in resolving the transfer conflicts.

There is a restriction of one transfer at a time for a single common-bus system. This means that other processors are busy with internal operations or remain useless waiting for the bus when one processor is interacting with the memory.

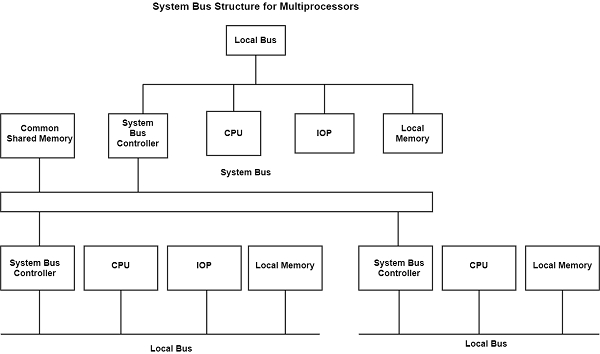

The system processors are kept busy by the execution of multiple separate buses, to allow multiple bus transfers simultaneously. However, this leads to an increase in the system cost and complexity. The figure shows a more economical execution of a dual bus structure for multiprocessors.

In the figure, we see that there are many local buses, and each bus is connected to its local memory, and one or more processors. Each local bus is linked to a peripheral, a CPU, or any mixture of processors. Each local bus is linked to a common system bus using a system bus controller.

The I/O devices linked to both the local I/O peripherals and the local memory is accessible to the local processor. All processors transfer the memory linked to the common system bus.

When an IOP is linked precisely to the system bus, the Input/Output devices connected to it are made accessible to all processors. There is only one processor that can interact with the shared memory, and different common resources by the system bus. All the multiple processors are busy connecting with their local memory and I/O devices.