Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is single shared bus in computer architecture?

One of the most famous interconnection networks is the single shared bus. Firstly, its organization is simply a generalization and extension of the buses employed in uniprocessors and some additional ones to solve the contention on the bus when several processors simultaneously want to use the shared bus. These lines are called arbitration lines and play a crucial role in the implementation of shared buses.

Secondly, the shared bus is a very cost-effective interconnection scheme. It can be raising the number of processors does not improve the price of the shared bus. However, the contention on the shared bus represents a strong limitation on the number of application processors.

Obviously, as the number of processors on the bus increases, the probability of contention also increases proportionally, reaching a point when the whole bandwidth of the bus is exhausted by the processors, and hence, adding a new processor will not cause any potential speed-up in the multiprocessor. One of the main design issues in shared bus multiprocessors is the enhancement of the number of applicable processors by different methods.

There are the three most important techniques are as follows −

- It can be introducing private memory.

- It can be introducing coherent cache memory.

- It can be introducing multiple buses.

Without these improvements, the applicable number of processors is in the range of 3-5. By introducing private memory and coherent cache memory, the number of processors can be increased by an order of magnitude up to 30 processors. Bus hierarchies open the way to constructing scalable shared memory systems based on bus interconnection.

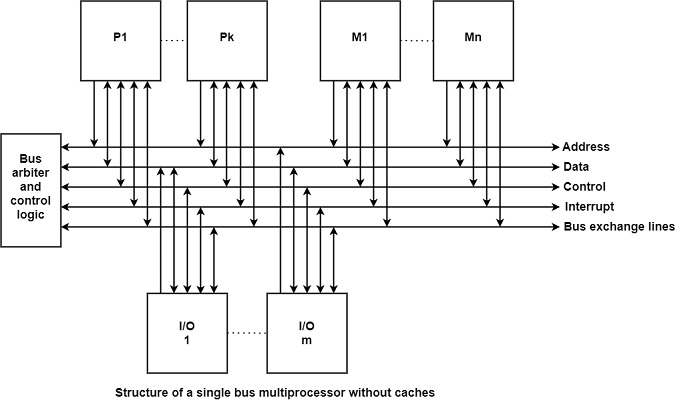

The typical structure of a single bus multiprocessor without coherent caches is shown in the figure. The new component of the system, relative to a uniprocessor, is the bus arbiter logic which has the role of allocating the bus in the case of several simultaneous bus requests, and the extra bus exchange lines supporting the work of the arbiter.

The bus exchange lines comprise typically one or more bus request lines using which the processors or other temporary bus masters can request bus allocation for their transfer. According to the state of the bus request lines and the applied bus allocation policy, the arbiter grants one of the requesters via the grant lines.

A memory write access need two phases that are as follows −

The address and data are transferred i.e., bus to the memory controller.

The memory write operation including parity check, error correction, and so on is executed by the memory controller.

Although the uniprocessor and multiprocessor buses are very similar. There is an important difference in their mode of operation. Uniprocessor and first-generation multiprocessor systems use locked buses. The second-generation multiprocessor used pended buses.

A memory read can access three phases are as follows −

The address is transferred via bus to the memory controller.

The memory read operation is executed by the memory controller.

The data is transferred via bus to requesting processor.