Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is multiple shared bus in computer architecture?

The limited bandwidth of the single shared bus represents a major limitation in building scalable multiprocessors. There are several ways to increase the bandwidth of the interconnection network. A natural idea is to multiply the number of buses, like the processors and memory units. Four different ways have been proposed for connecting buses to the processors, memory units and other buses are as follows −

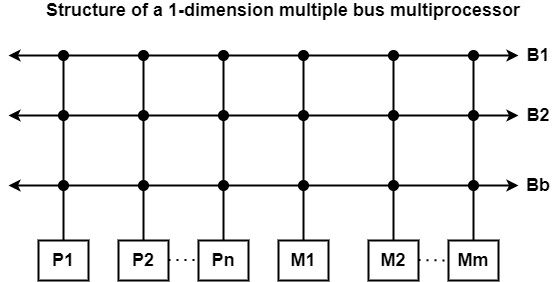

1-dimensional multiple bus system − The simplest generalization of the single bus system towards a multiple bus system is the 1-dimension multiple bus system as shown in the figure. This approach leads to a typical uniform memory access (UMA) machine where any processor can access any memory unit through any of the buses.

The employment of the 1-of-N arbiters is not sufficient in such systems. Arbitration is a two-stage process in 1-dimension multiple bus systems. First, the 1-of-n arbiters (one per memory unit) can resolve the conflict when multiple processors need unshared access to a similar shared memory unit.

After the first stage m (out of n) processors can get access to one of the memory units. However, when the multiple buses (b) is less than the number of memory units (m), the second stage of arbitration is required where an additional b-of-m arbiter is employed to assign buses to those processors that strongly retrieved access to a memory unit.

2 or 3 dimension bus systems − A further generalization of the 1-dimension multiple buses is the introduction of the second and third dimensions. In these systems, multiple buses compose a grid interconnection network. Each processor node is linked to a row bus and a column bus.

Processors along a row or column constitute a conventional single bus multiprocessor. The memory can be distributed in several ways. The most traditional approach is to attach memory units to each bus. The main problem of these architectures is the maintenance of cache coherency.

Cluster bus system − The third alternative to introduce several buses into the multiprocessor is the cluster architecture which represents a NUMA machine concept. The main idea of cluster architectures is that single bus multiprocessors, called clusters, are connected by a higher-level bus. Each cluster has its local memory.

The access time of a local cluster memory is much less than the access time of a remote cluster memory. Keeping the code and stacks in the cluster memory can significantly reduce the need to access remote cluster memory. However, it turned out that without cache support this structure cannot avoid traffic jams on higher-level buses.

Hierarchical bus system − There is another natural generalization of the single bus system is the hierarchical bus system where single bus ‘supernodes’ are connected to a higher-level bus via a higher-level cache or ‘supercache’.