Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is Binary Incrementer in Computer Architecture?

The increment micro-operation inserts one to a number in a register. For example, if a 4-bit register has a binary value 0110, it will go to 0111 after it is incremented. The increment micro-operation is performed by a 4-bit combinational circuit incrementer.

This micro-operation is simply performed with a binary counter. Each time the count allowed is active, the clock pulse transition increments the content of the register by one. There can be occasions when the increment micro-operation should be completed with a combinational circuit independent of a specific register. This can be done using half-adders connected in cascade.

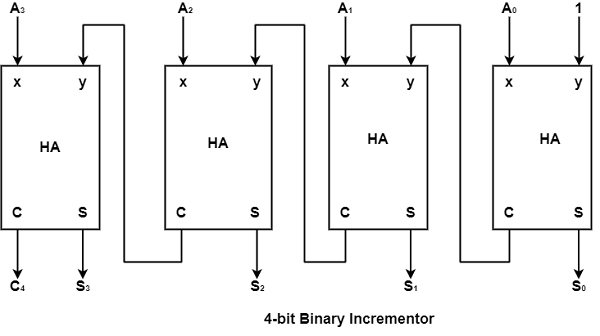

The diagram of a 4-bit combinational circuit incrementer is demonstrated in the figure.

One of the inputs to the least significant half-adder (HA) is connected to logic-1. The other input is linked to the least significant bit of the number to be incremented.

The output carry from one half-adder is linked to one of the inputs of the next-higher-order half-adder. The circuit gets the four bits from , A0 by A3 , inserts one to it, and produces the incremented output in S0 through S3.

The output carries C4 will be 1 only after incrementing binary 1111. It can also generate outputs S0 through S3, to go to 0.

The circuit of a diagram can be continued to an n-bit binary incrementer by continued the figure to contain n half-adders.

The least significant bit must have one input linked to logic-1. The other inputs receive the number to be incremented or the carry from the previous stage.