Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is Address Sequencing in Computer Architecture?

Microinstructions are saved in control memory in groups. These groups describe routines. Each computer instruction has its microprogram routine that can create micro-operations. These micro-operations can execute instructions. The hardware consists of controls for the address sequencing of the microinstructions of a similar routine. They also branch the microinstructions.

There are the following phases that the control has while implementing a computer instruction −

- When power is turned on, and address is initially loaded into the control address register. (This is the address of the first microinstruction).

- The control address register is incremented resulting in sequencing the fetch routine.

- After the fetch routine, the instruction is present in the IR of the computer.

- Next, the control memory retrieves the effective address of the operand from the routine.

- Thus, the mapping process appears from the instruction bits to a control memory address.

- It depends on the opcodes of instruction the microinstructions of the processor registers are generated. Each of these microinstructions has a separate microprogram routine stored.

- The instruction code bits are changed into the address where the routine is placed and is known as the mapping process. A mapping process transforms the microinstruction into a control memory address.

- Next, subroutines are called and processes are returned.

- After the completion of the routine, the control address register is incremented to sequence the instruction is implemented. It can also be based on the values of status bits in processor registers. External registers are needed through microprograms to save return addresses that use subroutines. After the instruction is performed, the control returns to the fetch routine. This is done by branching the microinstruction to the first address in the fetch routine.

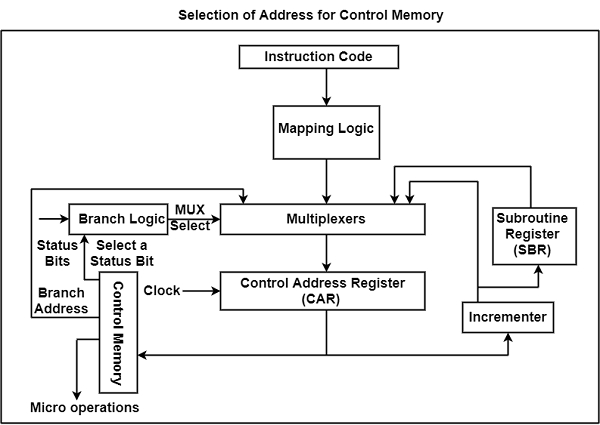

The diagram shows the block diagram of a control memory and its associated hardware to support in choosing the next microinstruction. The microinstruction present in the control memory has a set of bits that facilitate to start off the micro-operations in registers.

There are four different directions are showed in the figure from where the control address register recovers its address. The CAR is incremented by the incrementer and selects the next instruction. In multiple fields of microinstruction, the branching address can be determined to result in branching.

It can specify the condition of the status bits of microinstruction, conditional branching can be applied. A mapping logic circuit can share an external address. A special register can save the return address so that when the microprogram needs to return from the subroutine, it can need the value from the unique register.