Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

Interrupts of 6800

In Motorola M6800, there are two hardware interrupt pins. These pins are NMI and. IRQ These pins are active low input pins. The first one is non-maskable and the second one is maskable and lower priority interrupt. When the IM flag is 1, or CCR register is set, the interrupt is masked or disabled.

When the Micro processor enters into some Interrupt Service Subroutine (ISS), it uses SEI instruction to mask the interrupt even if the IRQ activated. The reverse action can be performed using the CLI instruction. It can unmask the interrupt.

When in the interrupt is occurred, the M6800 follows some task in the given sequence. This sequence is like below:

Complete the current instruction execution

Push the content of program Counter (PC)

Store the register content into the stack in a proper way.

Enable the InterruptMask (IM) flag

Jumps to the ISS which are stored in location FFFCH and FFFDH

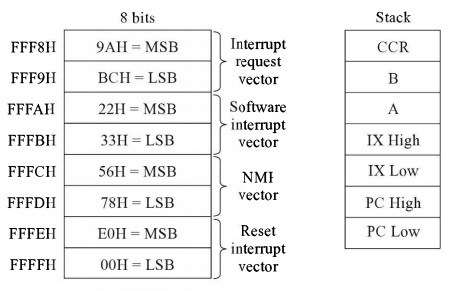

The memory space from FFF8H to FFFFH are divided into four parts. This location holds the upper and lower bytes of addresses for different interrupt vectors.

In the flowing diagram, we can find the interrupt vector locations and stack content while entering to the ISS.