Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

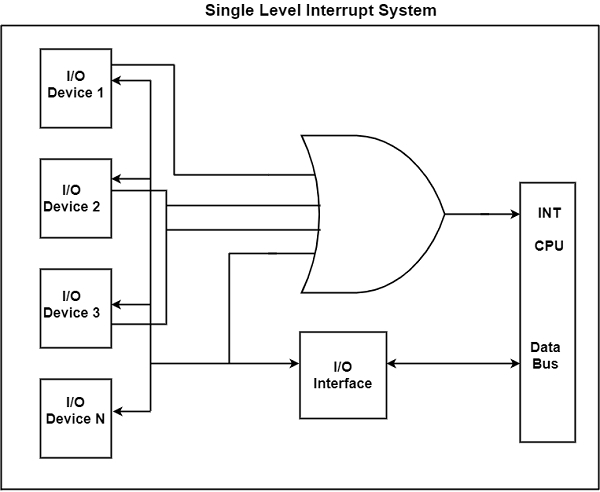

Discuss the Single Level Interrupts in Computer Architecture?

In single level interrupts, many devices can interrupt the processor at the same time to attend to their requests. But all the devices raise requests through a single input pin of the CPU. When interrupted, the CPU must identify the device that raised the request. Once the I/O port is identified, the CPU attends to the request of I/O device and then continues to carry out the task that it was performing before being interrupted.

In single-level interrupts, interrupt requests from all the devices are logically ORed and connected to the interrupt input of the processor. Hence, the interrupt request from any device is routed to the processor interrupt input. After the processor is interrupted, it identifies the requesting device by reading the interrupt status of each device.

The figure shows the equivalent circuit of the single interrupt line used in devices. All the I/O devices are connected to INTR through switches to the ground. A device closes its related switch to request an interrupt. When all the interrupt request signals from INTR1 to INTRn are inactive and all the switches are open, thus the voltage on the interrupt request will be equal to VDD.

When the device requests an interrupt by closing its switch, then the voltage line drops to 0, causing the interrupt request signal INTR to go to 1. The closing of one or more switching will cause the line voltage to drop to 0. This results in an INTR signal.