Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instruction type MOV r1, r2 in 8085 Microprocessor

In 8085 Instruction set, MOV is a mnemonic, which stands for "MOVe". In this instruction 8-bit data value in register r2 will be moved to the 8-bit register r1. Note that in 8085 instructions, as the first operand specifies the destination, and the second one the source, so here also r1 is destination register and r2 is the source register. This instruction uses register addressing for specifying the data. Here, "r1" and "r2"can be any one of the following registers.

r1, r2 = A, B, C, D, E, H, or L

As r1 can have any one of the seven values, and r2 can have any of the seven values, there are 7 × 7 = 49 opcodes for this type of instruction.

| Mnemonics, Operand | Opcode | Bytes |

|---|---|---|

| MOV A, A | 7F | 1 |

| MOV A, B | 78 | 1 |

| MOV A, C | 79 | 1 |

| MOV A, D | 7A | 1 |

| MOV A, E | 7B | 1 |

| MOV A, H | 7C | 1 |

| MOV A, L | 7D | 1 |

| MOV B, A | 47 | 1 |

| MOV B, B | 40 | 1 |

| MOV B, C | 41 | 1 |

| MOV B, D | 42 | 1 |

| MOV B, E | 43 | 1 |

| MOV B, H | 44 | 1 |

| MOV B, L | 45 | 1 |

| MOV C, A | 4F | 1 |

| MOV C, B | 48 | 1 |

| MOV C, C | 49 | 1 |

| MOV C, D | 4A | 1 |

| MOV C, E | 4B | 1 |

| MOV C, H | 4C | 1 |

| MOV C, L | 4D | 1 |

| MOV D, A | 57 | 1 |

| MOV D, B | 50 | 1 |

| MOV D, C | 51 | 1 |

| MOV D, D | 52 | 1 |

| MOV D, E | 53 | 1 |

| MOV D, H | 54 | 1 |

| MOV D, L | 55 | 1 |

| MOV E, A | 5F | 1 |

| MOV E, B | 58 | 1 |

| MOV E, C | 59 | 1 |

| MOV E, D | 5A | 1 |

| MOV E, E | 5B | 1 |

| MOV E, H | 5C | 1 |

| MOV E, L | 5D | 1 |

| MOV H, A | 67 | 1 |

| MOV H, B | 60 | 1 |

| MOV H, C | 61 | 1 |

| MOV H, D | 62 | 1 |

| MOV H, E | 63 | 1 |

| MOV H, H | 64 | 1 |

| MOV H, L | 65 | 1 |

| MOV L, A | 6F | 1 |

| MOV L, B | 68 | 1 |

| MOV L, C | 69 | 1 |

| MOV L, D | 6A | 1 |

| MOV L, E | 6B | 1 |

| MOV L, H | 6C | 1 |

| MOV L, L | 6D | 1 |

It occupies only 1-Byte in memory. MOV E, H is an example instruction of this type. It is a 1-Byte instruction. Suppose E register content is AB H, and H register content is 9C H. When the 8085 executes this instruction, the contents of E register will change to 9C H. This is shown as follows.

| Before | After | |

|---|---|---|

(E) |

AB H | 9C H |

(H) |

9C H | 9C H |

| Address | Hex Codes | Mnemonic | Comment |

|---|---|---|---|

| 2004 | 5C | MOV E, H | E |

Note that H register?s content has not been changed at all.Although Intel has called it a "move" instruction, but actually in reality it seems to be a"copy" instruction.

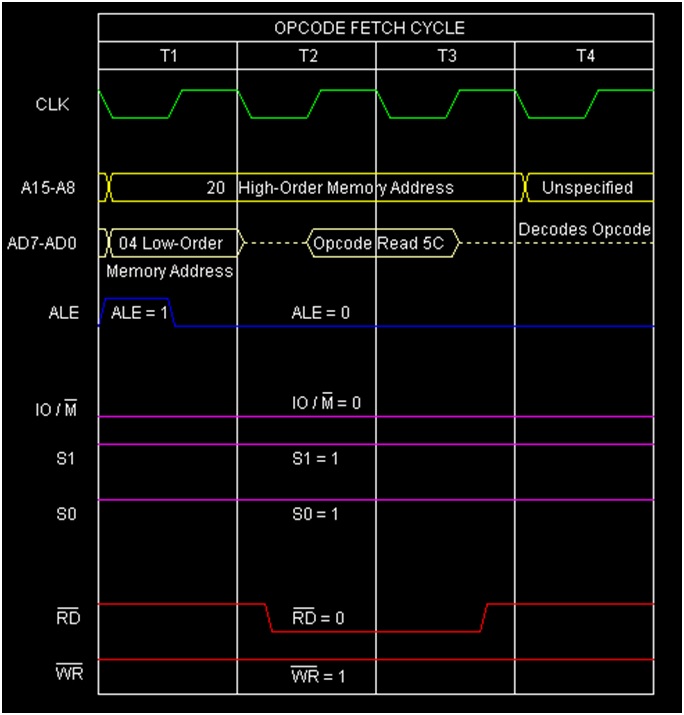

The timing diagram of MOV E, H instruction is as follows.

Summary − So this instruction MOV E, Hrequires 1-Byte, 1-Machine Cycles (Opcode Fetch) and 4 T-States for execution as shown in the timing diagram.