Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instruction type DCR R in 8085 Microprocessor

In 8085 Instruction set, DCR is a mnemonic, which stands for ?DeCRement? and ?R? stands for any of the following registers, or memory location M pointed by HL pair.

R = A, B, C, D, E, H, L, or M

This instruction is used to decrease the content of register R. Also we can say it will subtract 1 from the register R content. And the decremented value will be stored on to the register R itself. As it is an arithmetic instruction, so all flags, except Cy flag, are affected depending on the result. In those assembly language code where we require down counter, there we can use this instruction. So by design as mentioned, Cy flag is not affected by the execution of this instruction.

As R can have any of the eight register values, so eight opcodes for this type of instruction are possible. It occupies only 1-Byte in memory.

| Mnemonics, Operand | Opcode(in HEX) | Bytes |

|---|---|---|

| DCR A | 3D | 1 |

| DCR B | 05 | 1 |

| DCR C | 0D | 1 |

| DCR D | 15 | 1 |

| DCR E | 1D | 1 |

| DCR H | 25 | 1 |

| DCR L | 2D | 1 |

| DCR M | 35 | 1 |

Let us consider DCR M is an example instruction of this type. It is a 1-Byte instruction. Let us consider HL register pair is having initial content of 16-bit address as 4050H. And at memory location 4050H the content is ABH. So the result of execution of this instruction has been depicted in the following tracing table

| Before | After | |

|---|---|---|

(HL) |

4050H | 4050H |

(4050H) |

ABH | AAH |

(F) |

Any values | Cy=no change, AC=1,S=1,P=1,Z=0 |

| Address | Hex Codes | Mnemonic | Comment |

|---|---|---|---|

| 2005 | 35 | DCR M | (HL) = (HL) - 1 |

Actually, internally, 8085 performs this decrement operation by adding the 2's complement of 01H to ABH. So if the 4050H initial memory location content is 00H, then after execution of the instruction DCR M, the content would be FFH.

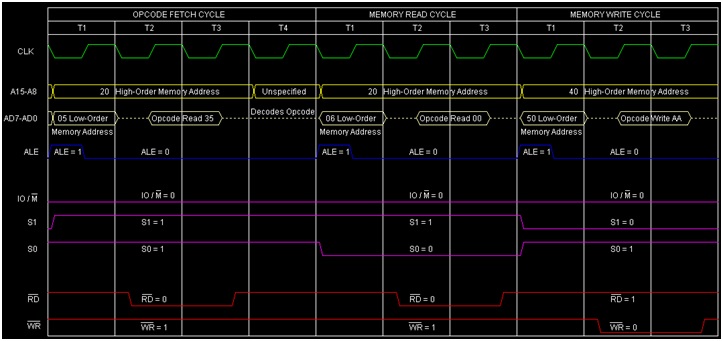

Summary − So this instruction DCR M requires 1-Bytes, 3-Machine Cycles (Opcode Fetch, Memory Read, Memory Write) and 10 T-States for execution as shown in the timing diagram.