Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instruction type INR R in 8085 Microprocessor

In 8085 Instruction set, INR is a mnemonic that stands for ?INcRement? and ?R? stands for any of the following registers or memory location M pointed by HL pair.

R = A, B, C, D, E, H, L, or M

This instruction is used to add 1 with the contents of R. So the previous value in R will get increased by amount 1 only. The result of increment will be stored in R updating its previous content. All flags, except Cy flag, are affected depending on the result thus produced. In different assembly language core, this instruction is used for looping or as a count. As R can have any of the eight values as mentioned, so there are eight opcodes possible for this type of instruction. It requires only 1-Byte in memory.

| Mnemonics, Operand | Opcode(in HEX) | Bytes |

|---|---|---|

| INR B | 04 | 1 |

| INR C | 0C | 1 |

| INR D | 14 | 1 |

| INR E | 1C | 1 |

| INR H | 24 | 1 |

| INR L | 2C | 1 |

| INR M | 34 | 1 |

Let us consider INR M as a sample instruction of this category. It is a 1-Byte instruction. Let us consider that HL register pair is holding the 16-bit value 4050H as 16-bit address. And 4050H location is holding value 05H. So after execution of the instruction INR M, the current content of location 4050H will become 06H. The tracing table of this instruction is as follows

| Before | After | |

|---|---|---|

(HL) |

4050H | 4050H |

(4050H) |

05H | 06H |

Flag Register (F) |

Any Value | Cy=no change,Ac=0,S=0,P=1,Z=0 |

| Address | Hex Codes | Mnemonic | Comment |

|---|---|---|---|

| 2005 | 34 | INR M | (HL) = (HL) + 1, i.e. 4050H memory locations content will be increased by 1 as HL register pair is having 16-bit address 4050H |

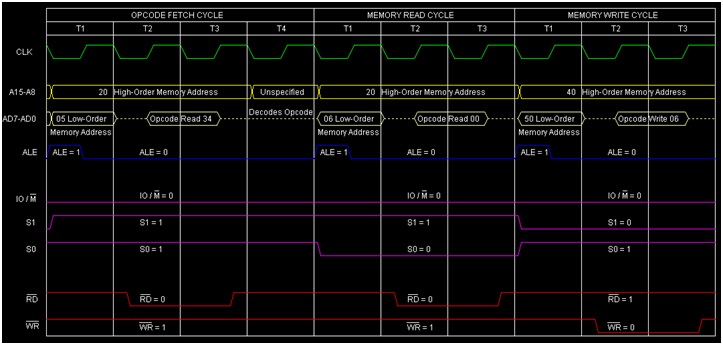

Here is the timing diagram of the execution of the instruction INR M

Summary − So this instruction INR M requires 1-Byte, 3-Machine Cycles (Opcode Fetch, Memory Read, Memory Write) and 10 T-States for execution as shown in the timing diagram.