Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is interpretation of sequential consistency of instruction execution?

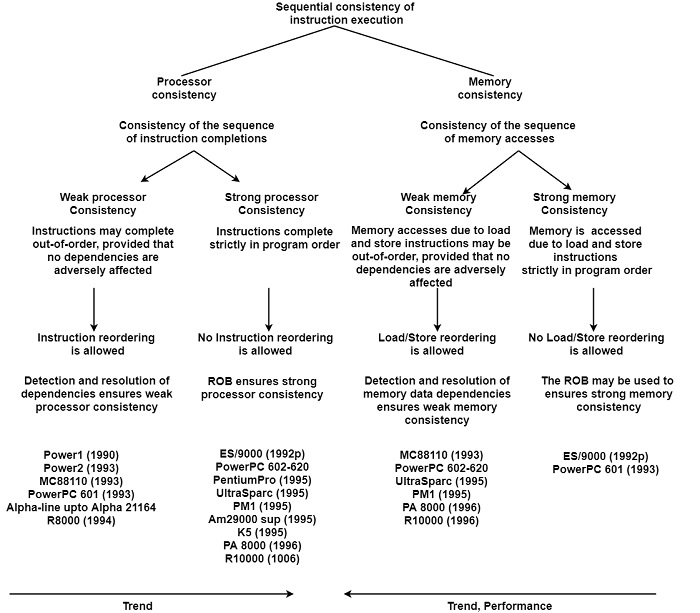

Sequential consistency of instruction execution associates with two techniques such as first to the order in which instructions are finished and second to the order in which memory is created because of the load and store instruction or memory references of other instructions as shown in the figure.

The term processor consistency indicates the consistency of instruction completion with sequential instruction execution. Superscalar processors preserve either a weak or strong consistency.

A weak processor consistency means that instructions can complete out-of-order, provides that no data dependencies are satisfied. In this case, instructions may be reordered by the processor only if no dependencies are violated. To achieve this, data dependencies have to be detected and appropriated resolved during superscalar execution.

In the case of strong processor consistency, instructions are forced to complete in strict program order. Usually, this is achieved by employing a reorder buffer (ROB). The ROB is a very practical tool as it can also be used to implement renaming and shelving as well, and ROB is now widely used in superscalar processors.

The other aspect of superscalar instruction execution is whether memory accesses are performed in the same order as in a sequential processor. This aspect is termed memory consistency.

The memory consistency is weak if memory accesses may be out of order compared with strict sequential program execution. However, data dependencies must not be violated. In other words, weak consistency allows load/store reordering provided that dependencies, particularly memory data dependencies, are detected and resolved.

The other alternative is strong memory consistency, in which memory accesses occur strictly in program order. Strong memory consistency forbids any load/store reordering.

The sequential consistency model of a processor integrates both aspects. It specifies the kind of consistency maintained by the processor and by the memory. Thus, by taking into account both aspects of processor and memory consistency, it arrives at four possible sequential consistency models.

These are the WW, WS, SW, and SS consistency models, where the first character refers to the type of processor consistency (Weak/Strong) and the second type of memory consistency (Weak/Strong).