Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is design space of instruction dispatch?

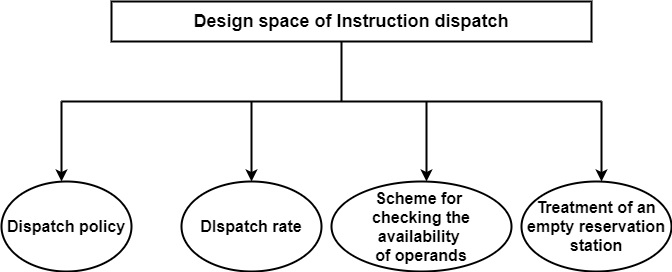

The design space of instruction dispatch is complex. In some respects, it resembles that of instruction issue but it has two additional aspects, as shown in the figure.

Dispatch Policy − The dispatch policy can be considered as a scheduling policy consisting of the components as −

Selection Rule − The selection rule specifies when instructions are studied executable. Let us take it for granted that renaming is employed and unresolved conditional transfer instructions are managed by speculative branch processing.

Arbitration Rule − It can also need an arbitration rule for the case when more instructions are eligible for execution that can be disseminated in the next cycle. Most processors use a straightforward arbitration rule that prefers ‘older’ instruction over ‘younger’ ones. Power1, Power2, PowerPC 620, PM1 (Sparc64), and PentiumPro are examples that use this arbitration rule.

Dispatch Order − The dispatch order specifies whether a non-executable instruction avoids all subsequent instructions from being dispatched.

Dispatch Rate − The design space needs additional components that determine how many instructions can be dispatched from each of the reservation stations, or the DRIS, per cycle. This component is called dispatch rate.

A shelving buffer must be capable of dispatching one instruction to any EU connected to it in each cycle. This is easier to achieve for group stations with two to three EUs than for a central station or a DRIS with a considerable number of EUs connected to it. The R10000, for instance, employs group reservation stations. Its FX reservation station can dispatch two instructions per cycle, one each to the EUs served.

Scheme for checking the availability of operands − The availability of operands has to be checked in two scenarios such as when the operands are fetched from the register file, a scheme is needed to check whether requested contents are available in the register file. A similar scheme is needed during instruction dispatch to check whether all the operands of the instructions held in the shelving buffers are available. It can make use of a technique that is generally employed to indicate the availability of register operands, called scoreboarding.

Treatment of an empty reservation station − When instruction arrives at an empty reservation station, the superscalar processor follows two different approaches. The straightforward approach is to process is an instruction in the same way as with a partially filled reservation station. However, entering instructions have to stay for at least one cycle in the empty station before they are dispatched. The Nx586 is an example of a processor that treats an empty reservation station in this way.

A more advanced approach for treating empty reservation stations is the use of bypasses. Here some additional circuitry permits instructions to bypass an empty station and be immediately forwarded to the EUs without any additional delay. The PowerPC 604 and PM1 (Sparc64) employ this more efficient approach.