- Digital Electronics - Home

- Digital Electronics Basics

- Types of Digital Systems

- Types of Signals

- Logic Levels And Pulse Waveforms

- Digital System Components

- Digital Logic Operations

- Digital Systems Advantages

- Number Systems

- Number Systems

- Binary Numbers Representation

- Binary Arithmetic

- Signed Binary Arithmetic

- Octal Arithmetic

- Hexadecimal Arithmetic

- Complement Arithmetic

- Base Conversions

- Base Conversions

- Binary to Decimal Conversion

- Decimal to Binary Conversion

- Binary to Octal Conversion

- Octal to Binary Conversion

- Octal to Decimal Conversion

- Decimal to Octal Conversion

- Hexadecimal to Binary Conversion

- Binary to Hexadecimal Conversion

- Hexadecimal to Decimal Conversion

- Decimal to Hexadecimal Conversion

- Octal to Hexadecimal Conversion

- Hexadecimal to Octal Conversion

- Binary Codes

- Binary Codes

- 8421 BCD Code

- Excess-3 Code

- Gray Code

- ASCII Codes

- EBCDIC Code

- Code Conversion

- Error Detection & Correction Codes

- Logic Gates

- Logic Gates

- AND Gate

- OR Gate

- NOT Gate

- Universal Gates

- XOR Gate

- XNOR Gate

- CMOS Logic Gate

- OR Gate Using Diode Resistor Logic

- AND Gate vs OR Gate

- Two Level Logic Realization

- Threshold Logic

- Boolean Algebra

- Boolean Algebra

- Laws of Boolean Algebra

- Boolean Functions

- DeMorgan's Theorem

- SOP and POS Form

- POS to Standard POS Form

- Minimization Techniques

- K-Map Minimization

- Three Variable K-Map

- Four Variable K-Map

- Five Variable K-Map

- Six Variable K-Map

- Don't Care Condition

- Quine-McCluskey Method

- Min Terms and Max Terms

- Canonical and Standard Form

- Max Term Representation

- Simplification using Boolean Algebra

- Combinational Logic Circuits

- Digital Combinational Circuits

- Digital Arithmetic Circuits

- Multiplexers

- Multiplexer Design Procedure

- Mux Universal Gate

- 2-Variable Function Using 4:1 Mux

- 3-Variable Function Using 8:1 Mux

- Demultiplexers

- Mux vs Demux

- Parity Bit Generator and Checker

- Comparators

- Encoders

- Keyboard Encoders

- Priority Encoders

- Decoders

- Arithmetic Logic Unit

- 7-Segment LED Display

- Code Converters

- Code Converters

- Binary to Decimal Converter

- Decimal to BCD Converter

- BCD to Decimal Converter

- Binary to Gray Code Converter

- Gray Code to Binary Converter

- BCD to Excess-3 Converter

- Excess-3 to BCD Converter

- Adders

- Half Adders

- Full Adders

- Serial Adders

- Parallel Adders

- Full Adder using Half Adder

- Half Adder vs Full Adder

- Full Adder with NAND Gates

- Half Adder with NAND Gates

- Binary Adder-Subtractor

- Subtractors

- Half Subtractors

- Full Subtractors

- Parallel Subtractors

- Full Subtractor using 2 Half Subtractors

- Half Subtractor using NAND Gates

- Sequential Logic Circuits

- Digital Sequential Circuits

- Clock Signal and Triggering

- Latches

- Shift Registers

- Shift Register Applications

- Binary Registers

- Bidirectional Shift Register

- Counters

- Binary Counters

- Non-binary Counter

- Design of Synchronous Counter

- Synchronous vs Asynchronous Counter

- Finite State Machines

- Algorithmic State Machines

- Flip Flops

- Flip-Flops

- Conversion of Flip-Flops

- D Flip-Flops

- JK Flip-Flops

- T Flip-Flops

- SR Flip-Flops

- Clocked SR Flip-Flop

- Unclocked SR Flip-Flop

- Clocked JK Flip-Flop

- JK to T Flip-Flop

- SR to JK Flip-Flop

- Triggering Methods:Flip-Flop

- Edge-Triggered Flip-Flop

- Master-Slave JK Flip-Flop

- Race-around Condition

- A/D and D/A Converters

- Analog-to-Digital Converter

- Digital-to-Analog Converter

- DAC and ADC ICs

- Realization of Logic Gates

- NOT Gate from NAND Gate

- OR Gate from NAND Gate

- AND Gate from NAND Gate

- NOR Gate from NAND Gate

- XOR Gate from NAND Gate

- XNOR Gate from NAND Gate

- NOT Gate from NOR Gate

- OR Gate from NOR Gate

- AND Gate from NOR Gate

- NAND Gate from NOR Gate

- XOR Gate from NOR Gate

- XNOR Gate from NOR Gate

- NAND/NOR Gate using CMOS

- Full Subtractor using NAND Gate

- AND Gate Using 2:1 MUX

- OR Gate Using 2:1 MUX

- NOT Gate Using 2:1 MUX

- Memory Devices

- Memory Devices

- RAM and ROM

- Cache Memory Design

- Programmable Logic Devices

- Programmable Logic Devices

- Programmable Logic Array

- Programmable Array Logic

- Field Programmable Gate Arrays

- Digital Electronics Families

- Digital Electronics Families

- CPU Architecture

- CPU Architecture

What is D Flip Flop?

What is D Flip Flop?

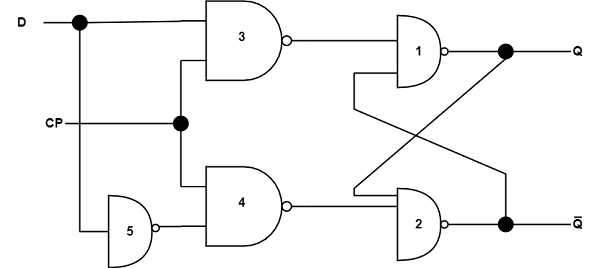

The D flip-flop is a clocked flip-flop with a single digital input 'D'. Each time a D flip-flop is clocked, its output follows the state of 'D'. The D Flip Flop has only two inputs D and CP. The D inputs go precisely to the S input and its complement is used to the R input.

Considering the pulse input is at 0, the outputs of gates 3 and 4 are at the 1 level and the circuit cannot convert state regardless of the value of D. The D input is sampled when CP = 1. If D is 1, the Q output goes to 1, locating the circuit in the set state. If D is 0, output Q goes to 0, and the circuit switches to a clear state.

Truth Table of D Flip Flop

The truth table for D flip-flop is as shown in the table.

| S | D | QN+1 |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

The logic symbol for the D flip-flop is shown in the figure.

The D flip flop obtains the destination from its capacity to manage data into its internal storage. This type of flip-flop is known as a gated D-latch. The CP input is provided given the destination G (for gate) to denote that this input allows the gated latch to create applicable data entry into the circuit.

The binary data present at the data input of the D flip flop is changed to the Q output when the CP input is allowed. The output follows the data input considering the pulse continues in its 1 state. When the pulse goes to 0, the binary data that was displayed at the data input at the time the pulse transition appeared is retained at the Q output until the pulse input is allowed again.

The truth table for the D flip flop is displayed in the table. It demonstrates that the next state of the flip flop is independent of the current state since QN+1 is similar to input D whether Q is similar to 0 or 1. This defines that an input pulse will change the value of input D into the output of the flip flop independent of the value of the output earlier the pulse was used.