Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What are the Instruction issue policies of the superscalar processor?

The following methods used in instruction issue policies such as the scalar processors, superscalar processors, and the broad picture covering both. While considering the most frequently used issue policies, it can reduce the design space of instruction issues by ignoring less important aspects.

First, for both scalar and superscalar processors, it can avoid issue order, because most processors employ an in-order issue. Moreover, it can discard issue alignment in the case of scalar and superscalar processors that make use of shelving.

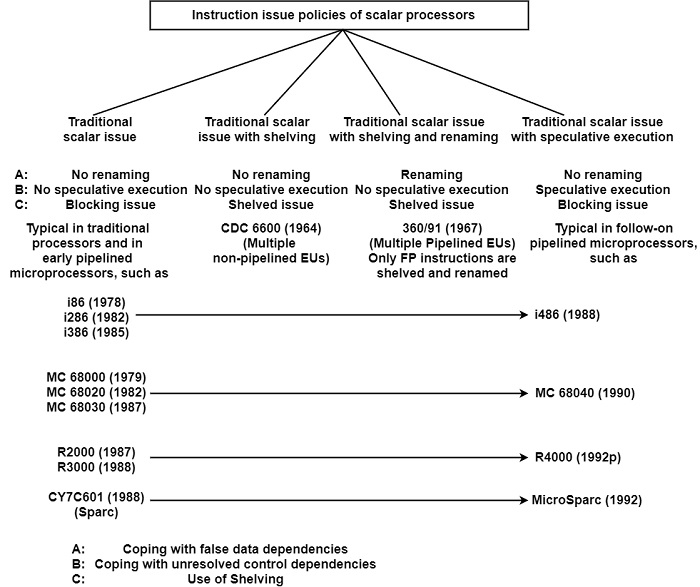

While considering instruction issue policies for scalar processors, it should be treated the three basic issue aspects such as whether to employ renaming, speculative execution, and shelving. Of the resulting eight possible issue policies, scalar processors use two principally, as displayed in the figure. They are the traditional scalar issue and its advancement with speculative execution.

Early non-pipelined processors issue instructions in sequence. This means that the next instruction was issued only after the earlier one had been done. These processors did not use renaming, speculative branch processing, or shelving.

Later, when ILP-processors with several execution units or pipelined processors appeared, the traditional scalar issue policy demonstrated too restrictive on performance. Two approaches were followed to ease this. One was introduced in the CDC6600, the other in the IBM 360/91. The CDC6600, a supercomputer of its time, was one of the first ILP processors. It accomplished high performance by introducing several non-pipelined, parallel working execution units.

The another approach was invented in the IBM 360/91. This processor was a more advanced ILP processor assembled of several pipelined floating-point execution units. It also employed shelving for floating-point instructions.

The simplest policy is the straightforward aligned superscalar issue. It does not allow renaming, needs to be aligned with direct issues, and employs speculative execution. As per this policy, instruction issue is blocked for data and resource dependencies, whereas control dependencies are met with speculative branch processing.

There is another set of processors that creates use of the straightforward superscalar issue, in a more progressive form, with an alignment-free issue. This extra feature provides increased performance. Examples of processors using this policy are the R8000, PA 7200, and UltraSparc.

The next issue policy is the straightforward superscalar issue policy with shelving that does not employ renaming, handles control dependencies with speculative execution, and introduces shelving. This scheme is used only in a few superscalar processors, including the MC88110 and R8000. Both these processors contain only partial shelving. The MC88110 shelves only store and conditional branches, whereas the R8000 shelves only floating-point instructions.