Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What are the types of issue blockages in computer architecture?

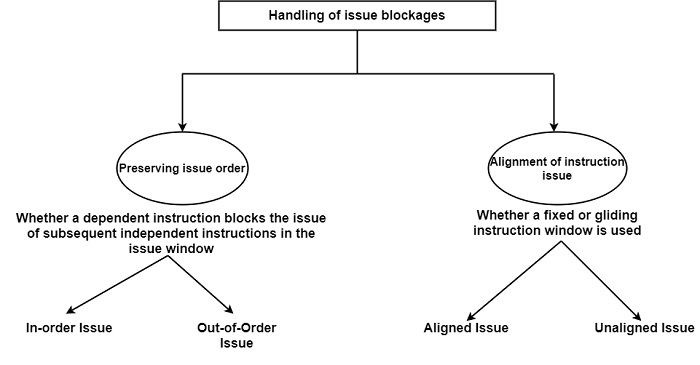

The handling of issue blockages can be broken into two types as displayed in the figure. The first aspect called preserving issue order specifies whether a dependent instruction blocks the issue of subsequent independent instructions in the issue window. The second aspect is the alignment of instruction issue. It decides whether a fixed or gliding issue window is used.

As shown in the figure, if a dependent instruction such as instruction b, blocks the issues of all subsequent instructions until the dependency is resolved, the issue order is known as ‘in-order’.

However, restricting subsequent independent instructions from the issue can extremely disrupt implementation. Hence, a few superscalar processors that employ the direct issue mode, including the MC88110 and the PowerPC 601, have introduced out-of-order issues.

The second aspect of handling issue blockages decides the alignment of instruction issues. It refers to whether the instruction is issued from a fixed window or a gliding window.

In the case of an aligned instruction issue, a fixed window is used. This defines that no instructions for the next window are treated as candidates for issue until all instructions in the current window have been issued.

Aligned instruction issue is typical for the first generation of superscalar processors, including the i960CA and Power1. But in the blocking-issue mode, aligned issues significantly decrease the effective issue rate. Therefore, several subsequent superscalar processors that still use the direct-issue mode introduced unaligned instruction issues.

Then a gliding window is employed whose width equals the issue rate. In every cycle, all instructions in the window are tested for dependencies. Independent instructions are issued from the window either in an in-order or in an out-of-order fashion. After the instruction issue, however, the window is refilled.

Unaligned instruction issue is classic for the second stream of superscalar processors that employ the direct-issue mode: the MC88110, MC68060, PA 7200, R8000, and UltraSparc. However, with the introduction of shelving, the motivation for using unaligned instruction issue has powerfully decreased. This is comprehensible because shelving delays dependency checks as far as instruction dispatching.

Therefore, while using shelving, instructions can be issued with almost no restrictions to the shelving buffers. The only condition that remains associate with trivial hardware requirements including the availability of shelving buffers, buses, etc. As an issue, modern superscalar processors that employ shelving have restored to aligned instruction issues. Examples of these are the PowerPC 603, PowerPC 604, PowerPC 620, and R10000.