Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

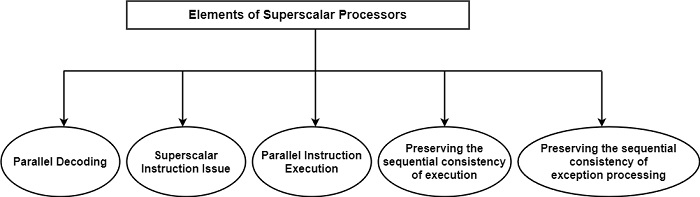

What are the key elements of Superscalar Processor?

Superscalar processing can be broken down into several particular tasks, which is shown in the figure. Superscalar processors can issue multiple instructions per cycle, the first task certainly is parallel decoding.

Decoding in superscalar processors is a significantly more complex task than in the case of scalar processors and evolves into even more sophisticated as the issue rate improves.

Higher issue rates can immensely extend the decoding cycle or can provide growth to various decoding cycles unless decoding is increased. An increasing technique of improvement is pre-decoding.

This is partial decoding implemented in advance of typical decoding, while instructions are loaded into the instruction cache. Most of the current processors use pre-decoding, including the PowerPC 620, PA 7200, PA 8000, UltraSparc, and R10000.

The function of superscalar processing is the superscalar instruction issue. A higher issue rate provides rise to higher processor implementation, but concurrently, it magnifies the restrictive result of control and data dependencies on the processor performance as well.

Control dependencies appear more repeatedly per issue in a superscalar processor, which issues several instructions in each cycle, than in a scalar processor. The frequent increase is roughly proportional to the issue rate of the processor.

As far as data dependencies are concerned, a higher issue rate can also strongly impede processor performance. Consider here that in a scalar processor, for instance in a pipelined processor, issue blockages due to dependencies can be avoided in most cases through the use of a parallel optimizing compiler. The compiler fills unused instruction channels, known as bubbles with separate instructions.

Thus, it can obtain higher performance, superscalar processors have introduced complex instruction issue policies, consisting of advanced techniques including shelving, register renaming, and speculative branch processing. As an effect, the instruction issue policy used turns into crucial for managing higher processor performance.

The next task is parallel instruction execution, which is a requirement of superscalar processing. However, while instructions are executed in parallel, instructions are generally completed out of order accordingly a sequentially operating processor. Due to this, specific means are required to have the logical consistency of program implementation. This task is generally known as the preservation of the sequential consistency of instruction execution.

Modern superscalar processors frequently achieve this by decoupling the generation of the results from writing them back into the particular register or memory areas. While the results are generated in parallel through the EUs, the program state is refreshed in a decoupled aspect sequentially in program order. As in the research for higher performance superscalar processors influence to provide increasingly more demanding.

Lastly, during instruction execution exceptions can increase. Therefore, sequential consistency is important and provides rise to the task known as the preservation of sequential consistency of exception processing.