Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

IO/M* PIN in 8085 Microprocessor

In Intel 8085 microprocessor I/O and memory operation are differentiated by IO/m` status signal.

IO/M` stands for ‘input-output/memory`’. When IO/M` is logic 0, it means that the address sent out by the processor is for addressing a memory location. When IO/M` is logic 1, it means that the address sent out by the processor is for addressing an I/O port.

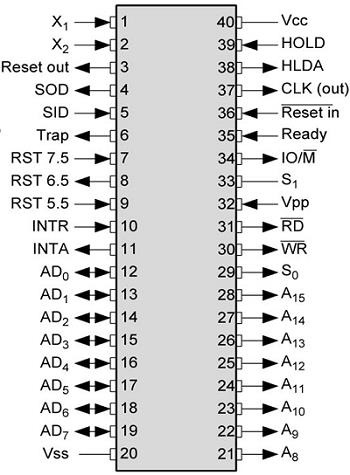

Fig: Pin diagram of 8085

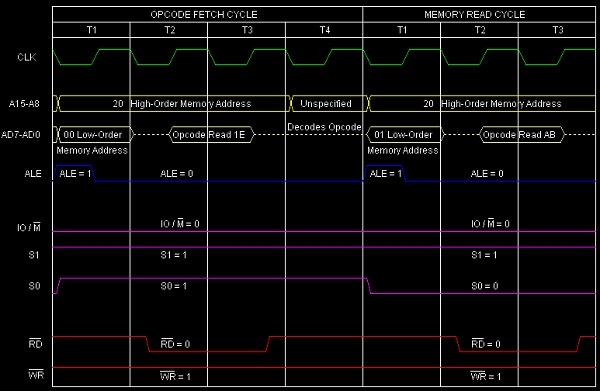

Let us consider this following example and also the voltage level at IO/M* pin. If we consider instruction MVI E, ABH then it means that ABH will be moved or copied to the register E. And as a result the previous value of E will get over written.

| Address |

Hex Codes |

Mnemonic |

Comment |

|---|---|---|---|

| 2000 |

1E |

MVIE, ABH |

E ← ABH |

| 2001 |

AB |

|

ABH as operand |

This instruction will have seven T-states as shown below.

Summary − So this instruction MVI E, ABH requires 2-Bytes, 2-Machine Cycles Opcode Fetch and Memory Read) and 7 T-States for execution as shown in the timing diagram.