Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What are the various approaches for branch handling in computer architecture?

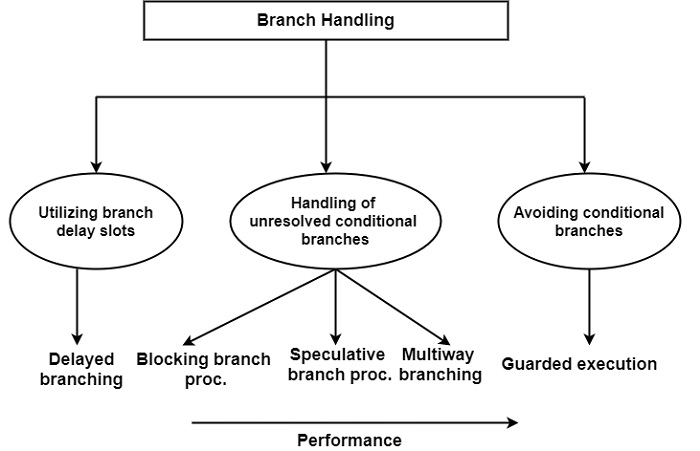

Processors use a large variety of approaches and techniques for branch handling. Three methods give an increase to the basic methods of in-branch handling. These are as follows −

whether branch delay slots are used

how unresolved conditional branches are handled

whether the architecture provides represents to prevent conditional branches.

The fundamental approaches to branch handling reflect these questions. According to how to branch handling responds to these questions it can determine delayed branching, blocking and speculative branch processing, multiway branching, and guarded execution.

The first method is whether branch delay slots are used. The simple branch handling generally results in one or two wasted pipeline cycles, known as bubbles, after each branch instruction. With delayed branching, alternatively, unutilized bubbles are filled until possible with executable instructions.

The second method is responsible for how unresolved conditional branches are handled. The processor can use one of three basic techniques. When unresolved conditional branches block the processing of branches until the particular condition can be computed, it can be concerned with blocking branch processing.

Early pipelined processors such as the MC 68020, MC 68030, and 80386 employed this ineffective way of branch handling.

The other method to cope with unresolved conditional branches is to facilitate speculative branch processing. In this case, for each unresolved conditional branch, a prediction is built for the result of the condition and processing extends along the guessed path.

The prediction is a guess as to whether the branch is expected to be taken or not, that is, whether the sequential or the taken path is expected to be followed. After resolution of the specified condition, the guess is determined. If it proves right, the process is extended.

If the guess is wrong, all speculatively executed instructions are rejected and the execution is sustained along the right path. Speculative branch processing is the prevailing approach at present. It is widely used in recent ILP-processors, especially in superscalar ones.

The last circumstance for handling unresolved conditional branches is to follow both possible implementation paths and reject the incorrect path after resolution of the particular condition. This method is known as multiway branching and has been used in some unproved or prototype VLIW machines.

The third and final method of branch handling is whether the architecture supports appropriate means to prevent conditional branches. If there are such means applicable, it can have guarded execution. In a sense, control dependencies are restored by data dependencies.

Although guarded execution probably has the highest performance potential among the schemes overviewed, it also has crucial drawbacks. It requires either a significant extension to or a redefinition of the instruction set architecture. In VLIW architectures, although a few main-line architectures also provide guarded instructions to some extent such as the HP PA, DEC Alpha, and SPARC V9 architectures.