Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

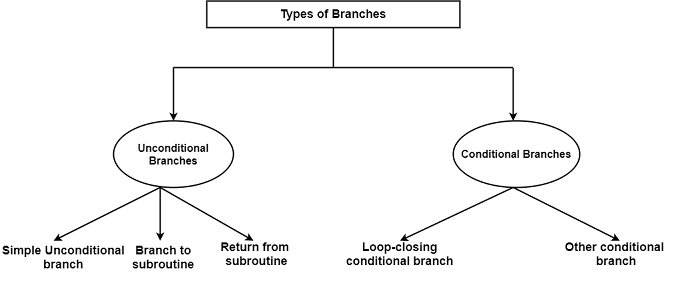

What are the various types of branches?

A branch in a computer program is an instruction that communicates a device to start implementing several instructions instead of simply performing the instructions in order. In high-level languages, these are defined as flow control phases and are established into the language. In assembly programming, branch instructions are established into a CPU.

Branches are used to transmission control, unconditionally or conditionally, to a stated position of the program. Unconditional branches are continually taken. In contrast, conditional branches contain a condition and thus are either taken or not taken, based on either the particular condition is true or false.

As shown in the diagram, it can display three types of unconditional branches − simple conditional branches, branches to a subroutine, and returns from subroutines. Simple unconditional branches do not store the return address whereas branches to subroutines do.

Returns from subroutines are dedicated unconditional branches implementing a control transfer to the stored return address. In nested subroutines, while branching to and returning from the single sub-routines, the return addresses are stored and utilized in a last-in-first-out (LIFO) manner.

A specific type of conditional branch is the loop-closing conditional branch. These branches are backward branches that are taken for all but the final iteration of a loop. Specific architectures offer means to provide the implementation of loop-closing branches. For instance, several architectures specify a count register that can be used as a loop counter, such as the PowerPC architecture.

An example of corresponding branch instructions as used in the DEC Alpha and PowerPC architectures. It is worth mentioning that the PowerPC architecture has a nice conception of branches, at least in two respects. First, the architecture does not have different branches and branches to subroutine instructions at the processor level.

All branches whether conditional or unconditional can be turned into a branch to subroutine instruction by setting a specified bit in the instruction encoding (called the LK bit) to 1. In this case, the return address will be saved in an architecturally defined register known as the link register.

A return from subroutine instruction is implemented simply as a special kind of branch where the target address is taken from the Link Register.

Second, the architecture handles conditional and unconditional branches in a unified way. Unconditional branches are simple variants of conditional branches with the condition always met. But, this method has a disadvantage, resulting in some off instruction mnemonics.