Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Edge-triggered Latches

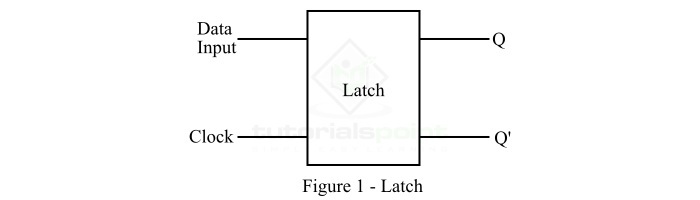

In digital circuits, a latch is a sequential logic circuit which has two stable states. Hence, a latch is also called as a bistable-multivibrator. A latch has capacity to store 1-bit of information. A latch has one or more inputs and two outputs. The outputs of a latch are specified by Q and Q'. Where, Q is the normal output of the latch and Q' is the inverted output. The block diagram of a latch is shown in Figure-1.

In this article, we will discuss about the edge triggered latches, their types, applications. So, let us start with the basic definition of the edge-triggered latch.

What is an Edge-Triggered Latch?

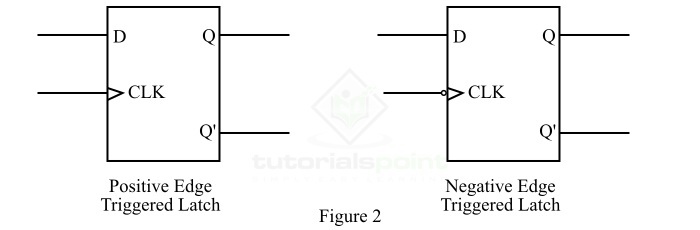

In digital circuits, an edge-triggered latch is a sequential circuit which is capable of storing 1-bit of information. It is called edge triggered latch because it updates its output state on the edge of the clock pulse. The block diagram of the edge triggered latch is shown in Figure-2 below.

Depending on the edge of the clock pulse to which the latch responds, the edge-triggered latches are classified into the following two types ?

Positive Edge-Triggered Latch

When the latch captures and stores the input information on the positive edge (edge that goes from low to high level) of the clock pulse is known as positive edge-triggered latch. Therefore, the output state of the positive edge triggered latch changes only when the clock pulse transit from low level to high level.

Negative Edge-Triggered Latch

When the latch captures and stores the input information on the negative edge (edge that goes from high level to low level) of the clock pulse is known as negative edge-triggered latch. Therefore, the output state of the negative edge triggered latch changes only when the clock pulse transit from high level to low level.

Operation of Edge-Triggered Latch

The working or operation of the edge triggered latch is quite simple. The edge triggered latch consists of a feedback path from output to input, and two cross-coupled NAND gates or NOR gates. It has two inputs, one is for data input and another one is for clock pulse.

When the clock pulse is low or high, the feedback path is open and the output of the latch remains in its previous state. When the clock pulse goes from low to high (or high to low), the feedback path be closed and the output state of the latch is then identified according to the state of the data input.

In the case of positive edge-triggered latch, the output state of the latch changes according to the data input when the clock pulse goes from low to high. This new state of the output is maintained as long as the clock pulse remains in the high state.

In the case of negative edge-triggered latch, the output state of the latch changes as per the data input when the clock pulse goes from high to low. This new state of the output is maintained as long as the clock pulse remains low.

Advantages of Edge-Triggered Latches

The major advantages of the edge-triggered latches are listed below ?

Edge triggered latches improve the timing control in digital circuits.

Edge triggered latches reduce the risk of timing violation in digital circuits.

Edge triggered latches improve the reliability of the circuit.

Edge triggered latches make the digital circuit less susceptible to the noise signals.

Edge triggered latches reduce the risk of errors in the output of a digital circuit.

Edge triggered latches consume relative less power.

Edge triggered latches improve the circuit stability.

Disadvantages of Edge-Triggered Latches

The major drawbacks of edge-triggered latches are given as follows ?

Edge triggered latches are relatively more complex to design and implement.

Edge triggered latches can be designed to operate within a limited range of frequency.

Edge triggered latches respond only when the clock transition takes place. This causes delayed response of the latch. Hence, edge triggered latches are not suitable where real-time response is required.

Edge triggered latches involve more complex clock management.

Applications of Edge-Triggered Latches

An edge-triggered latch is the basic memory element in several digital circuits. Some common applications of edge-triggered latches are listed below ?

Edge-triggered latches are used to construct registers which are used to store and shift data in digital systems.

Edge triggered latches are also employed for constructing counters used in digital systems to count events or cycles.

Edge triggered latches are also used to design memory elements like ROM, RAM, etc.

Edge triggered latches are also used in synchronous digital system as a crucial system component.

Edge triggered latches are used in communication systems for synchronization of data-transmission and data-reception.

Conclusion

This is all about edge-triggered latches, their construction, working, types, and applications. In conclusion, the edge triggered latch is a specially designed latch which response when the clock pulse goes from high to low or low to high. It is used as an important component in several digital systems to store 1-bit of data.