Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

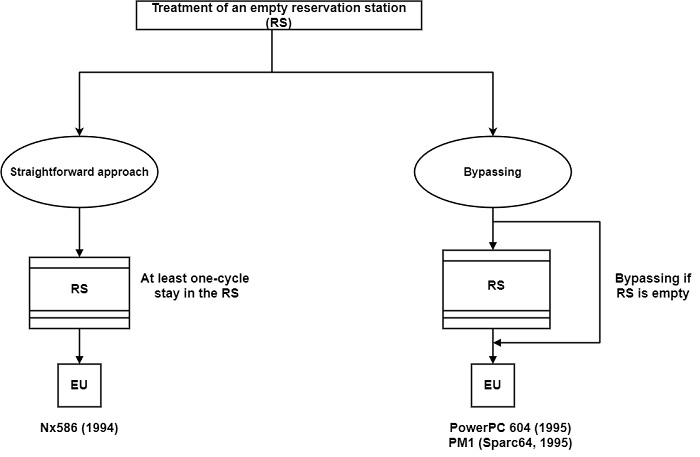

What are the treatments of an empty reservation station?

When instruction arrives at an empty reservation station, the superscalar processor follows two different approaches as shown in the figure. The straightforward approach is to process is an instruction in the same way as with a partially filled reservation station. However, entering instructions have to stay for at least one cycle in the empty station before they are dispatched. The Nx586 is an example of a processor that treats an empty reservation station in this way.

A more advanced approach for treating empty reservation stations is the use of bypasses. Here some additional circuitry permits instructions to bypass an empty station and be immediately forwarded to the EUs without any additional delay. The PowerPC 604 and PM1 (Sparc64) employ this more efficient approach.

Typical dispatch scheme

There are the following components of the dispatch scheme are as follows −

Most recent processors employ register renaming and speculative execution. Thus, the dataflow selection rule is used most often, with the oldest instruction preferred if arbitration is needed.

When operands are fetched during instruction dispatch most processors use the direct checking method. Alternatively, when operands are fetched during instruction issues, explicit status bits are typically maintained and checked for operand availability.

An empty reservation station is usually bypassed.

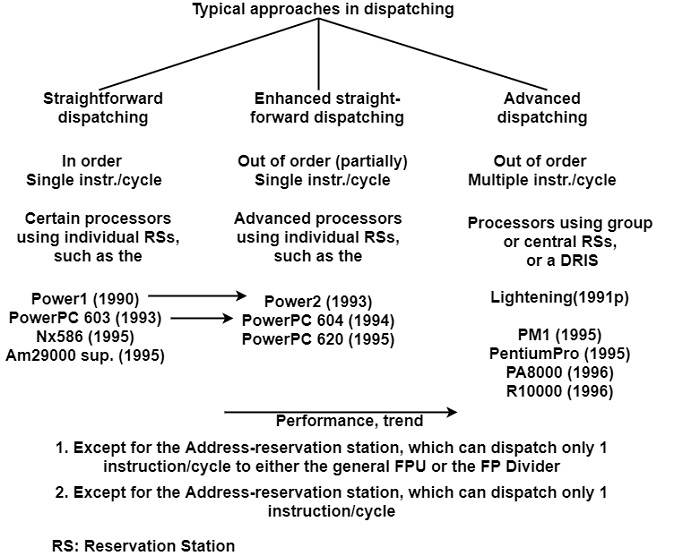

If we focus on the dispatch order and the dispatch rate, three typical approaches can be identified in recent superscalar processors, which are shown in the figure.

In straightforward dispatching, instructions are dispatched one at a time. In this simple approach an instruction that is not yet executable blocks further dispatching until this instruction becomes executable. Some processors using individual reservation stations employ this straightforward but inefficient approach.

The efficiency of this simple approach can be increased by introducing out-of-order dispatching for particular reservation stations. It can call this approach enhanced straightforward dispatching. In this case, the reservation station uses an out-of-order dispatch, and subsequent executable instructions can bypass an instruction that is not yet executable. This approach is typically employed in advanced processors using individual reservation stations.

Advanced dispatching is the most powerful. It allows out-of-order dispatch and is capable of forwarding multiple instructions per cycle to available EUs. This advanced dispatch policy is employed in processors with group reservation stations or with a central reservation station or a DRIS. Usually, subsequent processors of the same line tend to use more powerful approaches for dispatching.