Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Addressing modes of Z-80

Here we will see the addressing modes of the Zilog Z-80 Microprocessor. But at first we will discuss about the mnemonics of Z-80.

As we know there are many similarities between Intel 8085 and Zilog Z-80, so we can also find the similarity on the instructions. But in Z-80 the Mnemonics are slightly different. The Hex codes are same, but only the mnemonics are different. So, if we want to execute a program, which was written in the 8085 MPU, it will work fine. But Z-80 has many other instructions, which are not available in the 8085.

Here is the list of mnemonics of 8085 and Z-80, where the hex codes are same.

| 8085 Mnemonics | Z-80 Mnemonics |

|---|---|

| ADI/ACI d8 | ADD/ADC A, d8 |

| ADD/ADC M | ADD/ADC A, (HL) |

| ADD/ADC r | ADD/ADC A, r |

| DAD B/D/H/SP | ADD HL,BC/DE/HL/SP |

| SUI d8 | SUB d8 |

| SUB M | SUB (HL) |

| SBI d8 | SBC A, d8 |

| SBB M | SBC A, (HL) |

| SBB r | SBC A, r |

| CNC/CC/CZ/CNZ/CP/CM/CPO/CPE a16 | CALL C/NC/Z/NZ/P/M/PO/PE a16 |

| RNC/RC/RZ/RNZ/RP/RM/RPO/RPE | RET C/NC/Z/NZ/P/M/PO/PE |

| JMP a16 | JP a16 |

| JNC/JC/JZ/JNZ/JP/JM/JPO/JPE a16 | JP C/NC/Z/NZ/P/M/PO/PE a16 |

| PCHL | JP (HL) |

| RST 0/1/2/3/4/5/6/7 | RST 0/8/10H/18H/20H/28H/30H/38H |

| INR/DCR r/M | INC/DEC r/(HL) |

| INX/DCX B/D/H/SP | INC/DEC BC/DE/HL/SP |

| CMC/STC | CCF/SCF |

| CMP r/M | CP r/(HL) |

| CPI d8 | CP d8 |

| CMA | CPL |

| XCHG | EX DE,HL |

| XTHL | EX (SP), HL |

| HLT | HALT |

| IN a8 | IN A, (a8) |

| OUT a8 | OUT (a8), A |

| LDA a16 | LD A, (a16) |

| STA a16 | LD (a16), A |

| LDAX B/D | LD A, (BC)/(DE) |

| STAX B/D | LD (BC)/(DE), A |

| LHLD a16 | LD HL, (a16) |

| SHLD a16 | LD (a16), HL |

| MOV r1, r2 | LD r1, r2 |

| MOV M, r | LD (HL), r |

| MVI r/M, d8 | LD r/(HL), d8 |

| LXI B/D/H/SP, d16 | LD BC/DE/HL/SP, d16 |

| SPHL | LD SP, HL |

| PUSH/POP B/D/H/PSW | PUSH/POP BC/DE/HL/AF |

| RAL/RLC/RAR/RRC | RLA/RLCA/RRA/RRCA |

Now, we will see the addressing modes of the Z-80 Microprocessor.

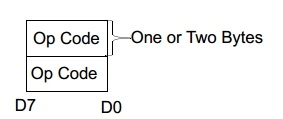

Immediate Addressing Mode

In this mode the byte, which is following the opcode is the actual operand. So, when we directly store some content into some register, it will be an example of immediate addressing mode.

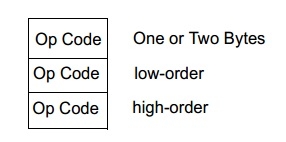

Immediate (Extended) Addressing Mode

It is same as the immediate addressing mode; the only difference is it takes 16-bit data as input after the opcode. To store some data into some register pair, we will use this kind of addressing modes.

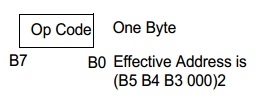

Modified Page Zero Addressing Mode

In this microprocessor, there are a 1-byte CALL instructions for any of eight locations in page zero of the memory. It acts like the restart operation. It sets the program counter to an effective address in Page zero.

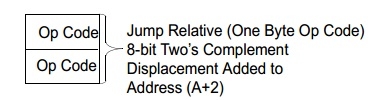

Relative Addressing Mode

In this mode, 1-byte data is provided to determine the displacement from the existing program to which a program jumps can occur. The displacement is signed 2’s complemented number.

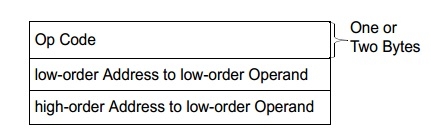

Extended Addressing Mode

In this mode, 2-byte data can be used after the opcode. These bytes can be an address for jump instructions, or an address where data can be stored.

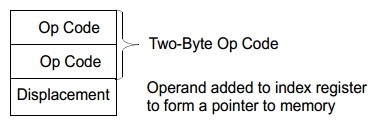

Indexed Addressing Mode

In this mode, the byte after opcode is containing the displacement, that is added to one of the two index register (IX or IY, specified by the instruction) to generate a pointer to memory. Here also the displacement is signed 2’s complemented number.

Register Addressing Mode

Some instructions use the CPU registers directly for an operation. Then the register addressing mode is used. For an example, if we want to load the content of register B into Register C, we have to use instructions which are belonging in this mode.

Implied Addressing Mode

The implied addressing mode refers to operation in which the opcode automatically selects one or more CPU registers to do some operations. Like for the arithmetic or logical operations, the opcode selects the accumulator (register A) as the destination of results.

Register Indirect Addressing Mode

When an instruction is using 16-bit register pair, which holds the address of some values in the memory, then that kind of instructions are under the register indirect addressing mode.

For an example, in different cases, we use the HL pair to hold some addresses, and when we want to update the data which is located at the address stored by the HL pair, we use register indirect mode.

Bit Addressing Mode

In the Z-80 MPU, there are some bit set, reset, test instructions. Using this mode, it can select any memory location or CPU register for bit operations through register, register indirect or indexed addressing modes.