Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

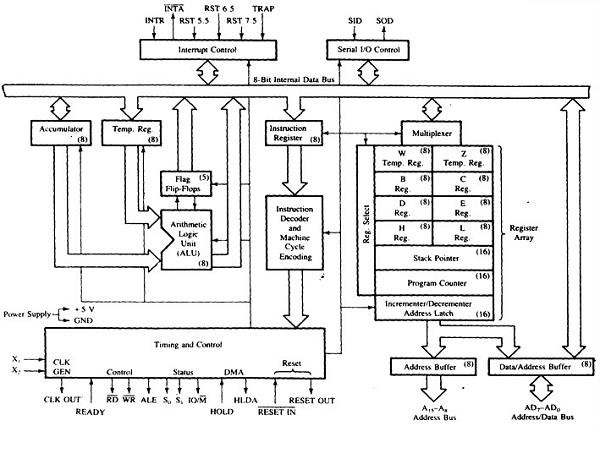

Registers of 8085 Microprocessor

It has eight addressable 8-bit registers: A, B, C, D, E, H, L, F, and two 16-bit registers PC and SP. These registers can be classified as −

General Purpose Registers

Temporary Registers: a) Temporary data register b) W and Z registers

Special Purpose Registers: a)Accumulator b) Flag registers c) Instruction register

Sixteen-bit Registers: a) ProgramCounter (PC) b) Stack Pointer (SP)

General Purpose Registers

Registers B, C, D, E, H, and L are general purpose registers in 8085 Microprocessor. All these GPRS are 8-bits wide. They are less important than the accumulator. They are used to store data temporarily during the execution of the program. For example, there is no instruction to add the contents of Band E registers. At least one of the operands has to be in A. Thus to add Band E registers, and to store the result in B register, the following have to be done.

Move to A register the contents of B register.

Then add A and E registers. The result will be in A.

Move this result from A register to B register.

It is possible to use these registers as pairs to store 16-bit information. Only BC, DE, and HLcan form register pairs. When they are used as register pairs in an instruction, the left register is understood to have the MS byte and the right register the LS byte. For example, in DE register pair, the content of the D register is treated as the MS byte, and the content of E register is treated as the LS byte.

Temporary Registers

(a)Temporary Data Register - The ALU has two inputs. One input is supplied by the accumulator and other from the temporary data register. The programmer cannot access this temporary data register. However, it is internally used for execution of most of the arithmetic and logical instructions.

(b) W and Z registers - Wand Z registers are temporary registers. These registers are used to hold 8-bit data during the execution of some instructions. These registers are not available for the programmer since 8085Microprocessor Architecture uses them internally.

Special Purpose Registers

(a) Register A(Accumulator) - Register A is an 8-bit register used in 8085 to perform arithmetic, logical, I/O & LOAD/STORE operations. Register A is quite often called as an Accumulator. An accumulator is a register for short-term, intermediate storage of arithmetic and logic data in a computer's CPU (Central Processing Unit).In an arithmetic operation involving two operands, one operand has to be in this register. And the result of the arithmetic operation will be stored or accumulated in this register. Similarly, in a logical operation involving two operands, one operand has to be in the accumulator. Also, some other operations, like complementing and decimal adjustment, can be performed only on the accumulator.

(b)Flag Register - It is a 3-bit register, in which five of the bits carry significant information in the form of flags: S (Sign flag), Z (Zero flag), AC(Auxiliary carry flag), P (Parity flag), and CY (carry flag); as shown in Fig. 1.2.

S-Sign flag - After the execution of arithmetic or logical operations, if bit D7 of the result is 1, the sign flag is set. In a given byte if D7 is1, the number will be viewed as a negative number. If D7 is U, the number will be considered as a positive number.

Z-Zero flag -The zero flag sets if the result of the operation in ALU is zero and flag resets if the result is non zero. The zero flags are also set if a certain register content becomes zero following an increment or decrement operation of that register.

AC-auxiliary Carry flag - This flag is set if there is an overflow out of bit 3 i.e. carry from lower nibble to higher nibble (D3 bit to D4 bit). This flag is used for BCD operations and it is not available for the programmer.

P-Parity flag - Parity is defined by the number of ones present in the accumulator. After arithmetic or logical operation, if the result has an even number of ones, i.e.even parity, the flag is set. If the parity is odd, the flag is reset.

CY-Carry flag - This flag is set if there is an overflow out of bit 7. The carry flag also serves as a borrow flag for subtraction. In both the examples shown below, the carry flag is set.

<p> Addition</p><p> 9BH -----> 1001 1011</p><p> +75 H -----> + 0111 0101</p><p> --------- -----------</p><p> Carry 1 10 H -----> 1 0001 0000</p><p> Subtraction</p> <p> 89H -----> 1000 1001</p><p> -AB H -----> - 1010 1011</p><p> --------- -----------</p><p> Borrow1 10 H -----> 1 1101 1110</p>

c) Instruction Register - In a typical processor operation, the processor first fetches the opcodeof instruction from memory (i.e. it places an address on the address bus and memory responds by placing the data stored at the specifiedaddress on the data bus). The CPU storesthis opcode in a register called the instruction register. Thisopcode is further sent to the instruction decoder to select one ofthe 256 alternatives.

4.SixteenBit Registers

a) Program counter (PC) - Program is a sequence of instructions. As mentioned earlier, microprocessor fetches these instructions from the memory and executes them The program counter is a special purpose register which, at a given time,stores the address of the next instruction to be fetched. Program Counter acts as a pointer to the next instruction. How processor increments program counter depends on the nature of the instruction;for one-byte instruction it increments program counter by one, for two-byte instruction it increments program counter by two and forthree-byte instruction it increments program counter by three such that program counter always points to the address of the next instruction.

In case of JUMP and CALL instructions, address followed by JUMP and CALL instructions is placed in the program counter. The processor then fetches the next instruction from the new address specified by JUMP or CALL instruction. In conditional JUMP and conditional CALL instructions, if the condition is not satisfied, the processor increments program counter by three so that it points the instruction followed by conditional JUMP or CALL instruction; otherwise processor fetches the next instruction from the new address specified by JUMP or CALL instruction.

b)Stack Pointer (SP) - The stack is a reserved area of the memory in the RAM where temporary information may be stored. A 16-bit stack pointer is used to hold the address of the most recent stack entry.

In the following figure depicts the architecture of 8085 microprocessor and with its register organization –