Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instruction type POP rp in 8085 Microprocessor

In 8085 Instruction set, with the mnemonic POP, we can pop out 2-Bytes from the top of the stack through rp i.e. register pair e.g. BC, DE, HL or AF. Here AF is a register pair formed with Flag and Accumulator registers and also known as PSW (Processor Status Word). In PSW, Accumulator is the MS Byte, and Flags register is the LS Byte.

| Mnemonics, Operand | Opcode(in HEX) | Bytes |

|---|---|---|

| POP B | C1 | 1 |

| POP D | D1 | 1 |

| POP H | E1 | 1 |

| POP PSW | F1 | 1 |

In the above mention Opcodes, 2-bits are occupied to mention the register pair. 2-bits can have 4 combinations. So 4 register pairs can be mentioned with POP. As mentioned earlier, they are BC, DE, HL and AF or PSW.

Note with LXI instruction, we are having 4 possible register pairs can be used i.e. BC, DE, HL and SP. So at the same time we can?t have SP and PSW applicable with the same instruction.

| rp Code | Register Pair |

|---|---|

| 0 0 | BC |

| 0 1 | DE |

| 1 0 | HL |

| 1 1 | SP or PSW, but never both at the same time. |

Let us consider the following example for better understanding of the operation of the instruction.

Here we are considering the instruction POP D which is an instruction falling in the category. As rp can have any of the four values, there are four opcodes for this type of instruction. It occupies only 1-Byte in memory. POP D is an example instruction of this type. It is a 1-Byte instruction. The result of execution of this instruction is shown below with an example.

| Before | After | |

|---|---|---|

(BC) |

AABBH | AABBH |

(SP) |

3FFEH | 4000H |

(3FFFH) |

AAH | AAH |

(3FFEH) |

BBH | BBH |

(DE) |

Any value | AABBH |

| Address | Hex Codes | Mnemonic | Comment |

|---|---|---|---|

| 2000 | 01 | LXI B, AABBH | Initializing BC register pair with AABBH |

| 2001 | BB | Low order Byte BBH | |

| 2002 | AA | High order Byte AAH | |

| 2003 | 31 | LXI SP,4000H | Initializing SP with 4000H |

| 2004 | 00 | Low order Byte 00H | |

| 2005 | 40 | High order Byte 40H | |

| 2006 | C5 | PUSH B | At 3FFFH, AAH and at 3FFEH,BBH will be moved |

| 2007 | D1 | POP D | Popping and initializing DE register pair with stack contents |

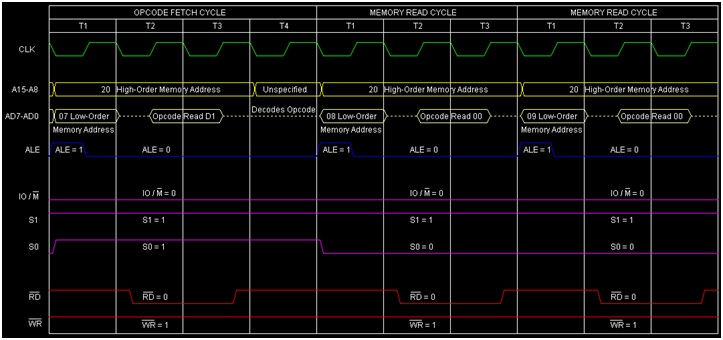

The timing diagram against this instruction POP D execution is as follows −

Summary − So this instruction POP requires 1-Byte, 3-Machine Cycles (Opcode Fetch, Memory Read, Memory Read) and 10 T-States for execution as shown in the timing diagram.