Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instruction Type LXI rp, d16 in 8085 Microprocessor

In the 8085 Instruction set there are four instructions, which belong to the type LXI rp, d16. These instructions are used to load the 16-bit address into the register pair. We can use this instruction to load data from memory location using the memory address, which is stored in the register pair rp. For an example, if the instruction is LXI H, FE50. It means that the FE50 is loaded into the HL register pair.

The rp can be BC, DE, HL or SP.

The LXI instructions and their Hex-codes are as follows.

| Mnemonics, Operand | Opcode (in HEX) | Bytes |

|---|---|---|

| LXI B | 01 | 3 |

| LXI D | 11 | 3 |

| LXI H | 21 | 3 |

| LXI SP | 31 | 3 |

Example

In this example, we can see how the LXI instruction can load 16-bit data into the Register Pairs.

Load 56FE into the DE register pair and ABCD into the HL register pair, exchange the content of DE and HL. And store the content of DE register pair into the location 8050 and 8051H.

| Address | Hex Codes | Mnemonic | Comment |

|---|---|---|---|

| 8000 |

11 FE 56 |

LXI D, 56FEH | Store 56FEH into the DE Register Pair. |

| 8003 |

21 CD AB |

LXI H, ABCDH | Store ABCDH into the HL Register Pair. |

| 8006 | EB | XCHG | Exchange the content of DE and HL |

| 8007 |

21 50 80 |

LXI H, 8050H | Load 8050H into the HL pair to store the result. |

| 800A | 72 | MOV M, D | Store the content of register D into the memory location. |

| 800B | 23 | INX H | Point HL to next source location |

| 800C | 73 | MOV M, E | Store the content of register E into the memory location. |

| 800D | 76 | HLT | Stop |

| Output | |

|---|---|

| Address | Value |

| 8050H | AB |

| 8051H | CD |

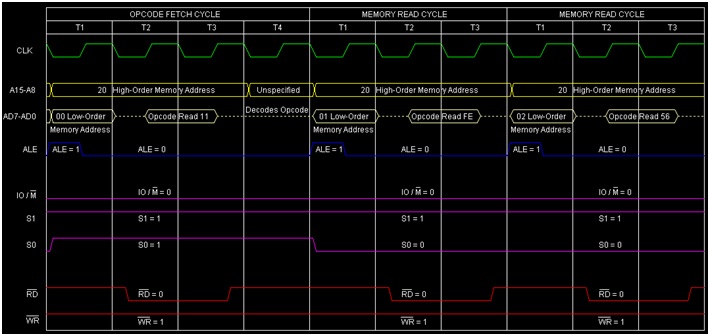

Following is the timing diagram of the instruction LXI D, 56FEH

Summary − So this instruction LXI D, 56FEH requires 3-Bytes, 3-Machine Cycles (Opcode Fetch, Memory Read, Memory Read) and 10 T-States for execution as shown in the timing diagram.