Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instruction type PUSH rp in 8085 Microprocessor

In 8085 Instruction set, PUSH rp instruction stores contents of register pair rp by pushing it into two locations above the top of the stack. rp stands for one of the following register pairs.

rp = BC, DE, HL, or PSW

As rp can have any of the four values, there are four opcodes for this type of instruction. It occupies only 1-Byte in memory.

| Mnemonics, Operand | Opcode(in HEX) | Bytes |

|---|---|---|

| PUSH B | C5 | 1 |

| PUSH D | D5 | 1 |

| PUSH H | E5 | 1 |

| PUSH PSW | F5 | 1 |

In the above mention Opcodes, 2-bits are occupied to mention the register pair. 2-bits can have 4 combinations. So 4 register pairs can be mentioned with POP. As mentioned earlier, they are BC, DE, HL and AF or PSW.

Note with LXI instruction, we are having 4 possible register pairs can be used i.e. BC, DE, HL and SP. So at the same time we can?t have SP and PSW applicable with the same instruction.

| rp Code | Register Pair |

|---|---|

| 0 0 | BC |

| 0 1 | DE |

| 1 0 | HL |

| 1 1 | SP or PSW, but never both at the same time. |

Let us consider PUSH B as an example instruction of this category. It is a 1-Byte instruction.

The result of execution of this instruction is shown below with an example.

| Before | After | |

|---|---|---|

(BC) |

AABBH | AABBH |

(SP) |

4000H | 3FFEH |

(3FFFH) |

Any value | AAH |

(3FFEH) |

Any value | BBH |

| Address | Hex Codes | Mnemonic | Comment |

|---|---|---|---|

| 2000 | 01 | LXI B, AABBH | Initializing BC register pair with AABBH |

| 2001 | BB | Low order Byte BBH | |

| 2002 | AA | High order Byte AAH | |

| 2003 | 31 | LXI SP,4000H | Initializing SP with 4000H |

| 2004 | 00 | Low order Byte 00H | |

| 2005 | 40 | High order Byte 40H | |

| 2006 | C5 | PUSH B | At 3FFFH, AAH and at 3FFEH,BBH will be moved |

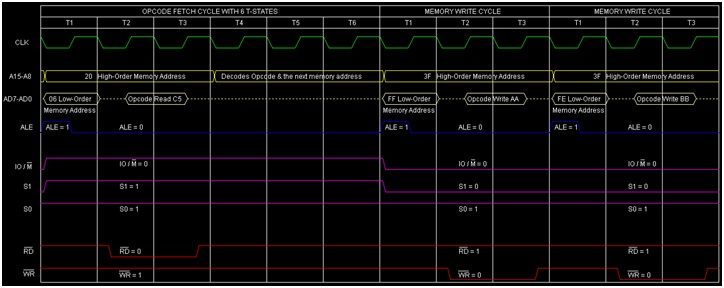

The timing diagram against this instruction PUSH B execution is as follows −

Summary − So this instruction PUSH B requires 1-Byte, 3-Machine Cycles (Opcode Fetch, Memory Write, Memory Write) and 12 T-States for execution as shown in the timing diagram.