Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instruction type INX rp in 8085 Microprocessor

In 8085 Instruction set, INX is a mnemonic that stands for "INcrementeXtended register" and rp stands for register pair. And it can be any one of the following register pairs.

rp = BC, DE, or HL

This instruction will be used to add 1 to the present content of the rp. And thus the result of the incremented content will remain stored in rp itself. Though it is an arithmetic instruction, note that, flag bits are not at all affected by the execution of this instruction. A register pair is generally used to store 16-bit memory address. If flag bits got affected during increment of a memory address, then it may cause problems in many cases. So as per design of 8085, flag bits are not getting affected by the execution of this instruction INXrp.

As rp can have any one of the three values, there are three opcodes for this type of instruction. It occupies only 1-Byte in memory.

| Mnemonics, Operand | Opcode(in HEX) | Bytes |

|---|---|---|

| INX B | 03 | 1 |

| INX D | 13 | 1 |

| INX H | 23 | 1 |

Let us consider INX B as a sample instruction falling in this category. As it is a 1-Byte instruction, so it will occupy single Byte location in the memory. Let us consider that the initial content of register pair BC is 4050H. So after execution of the instruction INX B, the new content of BC register pair would be 4051H. The result of execution of this instruction is shown below with the help of a tracing table −

| Before | After | |

|---|---|---|

(BC) |

4050H | 4051H |

| Address | Hex Codes | Mnemonic | Comment |

|---|---|---|---|

| 2003 | 03 | INX B | BC = BC + 1 |

We may think that INX B is similar to INR C in this example. But that is not true. As if the initial content of BCH be 1FFFH then after INX B instruction execution it would be 2000H not 1F00H.So, basically, INX instruction increments a 16-bit quantity, whereas INR increments an 8-bit quantity.

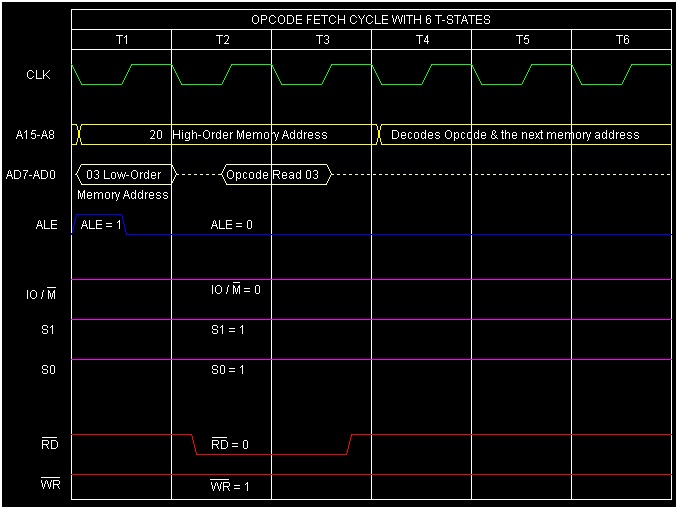

Here is the timing diagram of the instruction execution INX B as below −

Summary − So this instruction INX B requires 1-Byte, 1-Machine Cycle (Opcode Fetch) and 6 T-States for execution as shown in the timing diagram.