Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instructions to complement/set Cy flag in 8085 Microprocessor

In 8085 Instruction set,there are two instructions to control the Cy flag bit content. Thesemnemonics are STC and CMC. Both are 1-Byteinstructions. There hex codes are given in the following table –

|

Mnemonics,Operand |

Opcode(in HEX) |

Bytes |

| STC |

37 |

1 |

| CMC |

3F |

1 |

Using STC instruction we can set the Cy flag bit to 1 irrespective of itsprevious value. And using CMC instruction we can complement the current value of the Cy fag bit andresult will update the current Cy flag bit value. Here STC stands for “SeT the Carry flag” and CMC stands for “CoMplement the Carry flag”. Note that, there isno dedicated instruction in 8085 instruction set to reset the Cy flagbit. To resent the Cy flag bit we can execute STC and CMCinstructions sequentially in this order.

Intel 8085 also provides instructions to complement thecy flag, and set the cy flag to the 1 state. But it does not have aninstruction to reset the cy flag to 0. If it is desired to reset cyflag to 0, the method is to set it to 1 and then complement it.Notice that no other flag can be set or complemented.

|

Address |

Hex Codes |

Mnemonic |

Comment |

| 2000 |

37 |

STC |

Set the Cy flag bit to 1 irrespective of its previous value |

| 2001 |

3F |

CMC |

Complement the Cy flag bit. So here Cy ← complement of 1 = 0 will be the final value of Cy flag bit |

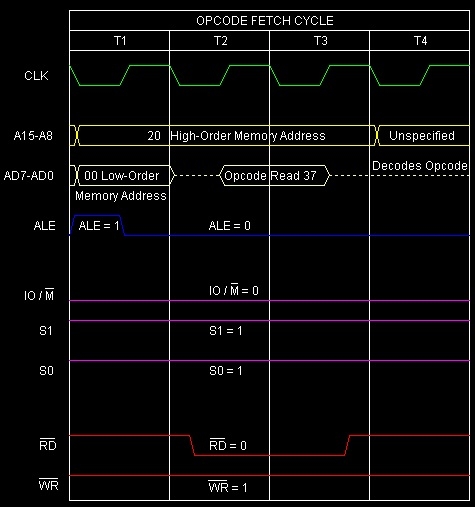

The timing diagram against this instruction STC execution is as follows –

Summary − So this instruction STC requires 1-Byte, 1-Machine Cycle (Opcode Fetch) and 4 T-States for execution as shown in the timing diagram.

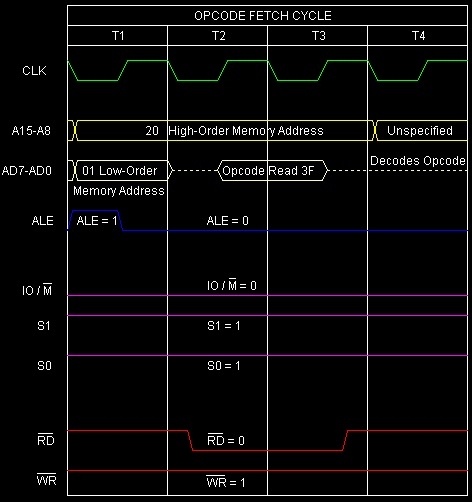

The timing diagram against this instruction CMC execution is as follows –

Summary − So this instruction CMC requires 1-Byte, 1-Machine Cycle (Opcode Fetch) and 4 T-States for execution as shown in the timing diagram.