- Data Comm & Networks Home

- DCN - Overview

- DCN - What is Computer Network

- DCN - Uses of Computer Network

- DCN - Computer Network Types

- DCN - Network LAN Technologies

- DCN - Computer Network Models

- DCN - Computer Network Security

- DCN - Components

- DCN - Connectors

- DCN - Switches

- DCN - Repeaters

- DCN - Gateways

- DCN - Bridges

- DCN - Socket

- DCN - Network Interface Card

- DCN - NIC: Pros and Cons

- DCN - Network Hardware

- DCN - Network Port

- Computer Network Topologies

- DCN - Computer Network Topologies

- DCN - Point-to-point Topology

- DCN - Bus Topology

- DCN - Star Topology

- DCN - Ring Topology

- DCN - Mesh Topology

- DCN - Tree Topology

- DCN - Hybrid Topology

- Physical Layer

- DCN - Physical Layer Introduction

- DCN - Digital Transmission

- DCN - Analog Transmission

- DCN - Transmission media

- DCN - Wireless Transmission

- DCN - Transmission Impairments

- DCN - Multiplexing

- DCN - Network Switching

- DCN - Circuit Switching

- DCN - Packet Switching

- DCN - Message Switching

- Data Link Layer

- DCN - Data Link Layer Introduction

- DCN - Data Link Control & Protocols

- DCN - RMON

- DCN - Token Ring Network

- DCN - Hamming Code

- DCN - Byte Stuffing

- DCN - Channel Allocation

- DCN - MAC Address

- DCN - Address Resolution Protocol

- DCN - Cyclic Redundancy Checks

- DCN - Error Control

- DCN - Flow Control

- DCN - Framing

- DCN - Error Detection & Correction

- DCN - Error Correcting Codes

- DCN - Parity Bits

- Network Layer

- DCN - Network Layer Introduction

- DCN - Network Addressing

- DCN - Routing

- DCN - Routing Table

- DCN - Internetworking

- DCN - Network Layer Protocols

- DCN - Routing Information Protocol

- DCN - Border Gateway Protocol

- DCN - OSPF Protocol

- DCN - Network Address Translation

- DCN - Network Address Translation Types

- Transport Layer

- DCN - Transport Layer Introduction

- DCN - Transmission Control Protocol

- DCN - User Datagram Protocol

- DCN - Congestion Control

- DCN - Open Loop Congestion Control

- DCN - Closed Loop Congestion Control

- DCN - Congestion Control Algorithms

- DCN - Token Bucket Algorithm

- DCN - TCP Tahoe Algorithm

- DCN - TCP Reno Algorithm

- DCN - TCP New Reno Algorithm

- DCN - TCP BIC Algorithm

- DCN - TCP CUBIC Algorithm

- DCN - TCP Service Model

- DCN - TLS Handshake

- DCN - TCP Vs. UDP

- Application Layer

- DCN - Session Layer

- DCN - Presentation Layer

- DCN - Application Layer Introduction

- DCN - Client-Server Model

- DCN - Application Protocols

- DCN - Network Services

- DCN - Virtual Private Network

- DCN - Load Shedding

- DCN - Optimality Principle

- DCN - Service Primitives

- DCN - Services of Network Security

- DCN - Hypertext Transfer Protocol

- DCN - File Transfer Protocol

- DCN - Secure Socket Layer

- Network Protocols

- DCN - ALOHA Protocol

- DCN - Pure ALOHA Protocol

- DCN - Sliding Window Protocol

- DCN - Stop and Wait Protocol

- DCN - Link State Routing

- DCN - Link State Routing Protocol

- Network Algorithms

- DCN - Shortest Path Algorithm

- DCN - Routing Algorithm

- DCN - Adaptive Routing Algorithms

- DCN - Non-Adaptive Routing Algorithms

- DCN - Leaky Bucket Algorithm

- Wireless Networks

- DCN - Wireless Networks

- DCN - Wireless LANs

- DCN - Wireless LAN & IEEE 802.11

- DCN - IEEE 802.11 Wireless LAN Standards

- DCN - IEEE 802.11 Networks

- Multiplexing

- DCN - Multiplexing & Its Types

- DCN - Time Division Multiplexing

- DCN - Synchronous TDM

- DCN - Asynchronous TDM

- DCN - Synchronous Vs. Asynchronous TDM

- DCN - Frequency Division Multiplexing

- DCN - TDM Vs. FDM

- DCN - Code Division Multiplexing

- DCN - Wavelength Division Multiplexing

- Miscellaneous

- DCN - Shortest Path Routing

- DCN - B-ISDN Reference Model

- DCN - Design Issues For Layers

- DCN - Selective-repeat ARQ

- DCN - Flooding

- DCN - E-Mail Format

- DCN - Cryptography

- DCN - Unicast, Broadcast, & Multicast

- DCN - Network Virtualization

- DCN - Flow Vs. Congestion Control

- DCN - Asynchronous Transfer Mode

- DCN - ATM Networks

- DCN - Synchronous Vs. Asynchronous Transmission

- DCN - Network Attacks

- DCN - WiMax

- DCN - Buffering

- DCN - Authentication

- DCN Useful Resources

- DCN - Quick Guide

- DCN - Useful Resources

- DCN - Discussion

Switches in Computer Networks

Switches

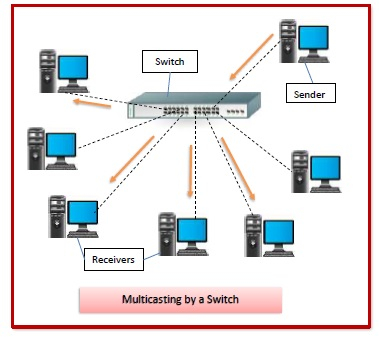

Switches are networking devices operating at layer 2 or a data link layer of the OSI model. They connect devices in a network and use packet switching to send, receive or forward data packets or data frames over the network.

A switch has many ports, to which computers are plugged in. When a data frame arrives at any port of a network switch, it examines the destination address, performs necessary checks and sends the frame to the corresponding device(s). It supports unicast, multicast as well as broadcast communications.

Features of Switches

-

A switch operates in the layer 2, i.e. data link layer of the OSI model.

-

It is an intelligent network device that can be conceived as a multiport network bridge.

-

It uses MAC addresses (addresses of medium access control sublayer) to send data packets to selected destination ports.

-

It uses packet switching technique to receive and forward data packets from the source to the destination device.

-

It is supports unicast (one-to-one), multicast (one-to-many), and broadcast (one-to-all) communications.

-

Transmission mode is full duplex, i.e. communication in the channel occurs in both the directions at the same time. Due to this, collisions do not occur.

-

Switches are active devices, equipped with network software and network management capabilities.

-

Switches can perform some error checking before forwarding data to the destined port.

-

The number of ports is higher 24/48.

Types of Switches

There are variety of switches that can be broadly categorised into 4 types

-

Unmanaged Switch These are inexpensive switches commonly used in home networks and small businesses. They can be set up by simply plugging in to the network, after which they instantly start operating. When more devices needs to be added, more switches are simply added by this plug and play method. They are referred to as u managed since they do not require to be configured or monitored.

-

Managed Switch These are costly switches that are used in organisations with large and complex networks, since they can be customized to augment the functionalities of a standard switch. The augmented features may be QoS (Quality of Service) like higher security levels, better precision control and complete network management. Despite their cost, they are preferred in growing organizations due to their scalability and flexibility. Simple Network Management Protocol (SNMP) is used for configuring managed switches.

-

LAN Switch Local Area Network (LAN) switches connects devices in the internal LAN of an organization. They are also referred as Ethernet switches or data switches. These switches are particularly helpful in reducing network congestion or bottlenecks. They allocate bandwidth in a manner so that there is no overlapping of data packets in a network.

-

PoE Switch Power over Ethernet (PoE) switches are used in PoE Gogabit Ethernets. PoE technology combine data and power transmission over the same cable so that devices connected to it can receive both electricity as well as data over the same line. PoE switches offer greater flexibility and simplifies the cabling connections