Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

What is Register Renaming?

Register renaming is a standard approach for eliminating false data dependencies, such as WAR and WAW dependencies, between register data. It was first suggested by Tjaden and Flynn in 1970.

They intended to use register renaming for a definite set of instructions that compare more or less to the class of load instructions, although it does not use the phrase ‘renaming’. Keller (1975) introduced the designation ‘register renaming’ and interpreted it for all suitable instructions.

Register Renaming presumes the three-operand instruction format. To illustrate this precondition, let us consider a two-operand instruction, say

ad r1, r2

with the interpretation

r1←(r1)+(r2)

In the two instruction format, the result is written back in place of one of the source operands, in the example in the place of r1. However, for the renaming of the destination, a register different from that containing a source operand (r1) has to be used, say r11. Thus, after renaming we get

r11←(r1)+(r2)

This means that the renaming of two-operand instruction always ends up as three-operand instruction. As a consequence, two-operand instructions can only be renamed using an internal two to three operand conversion.

Implementation of Register Renaming

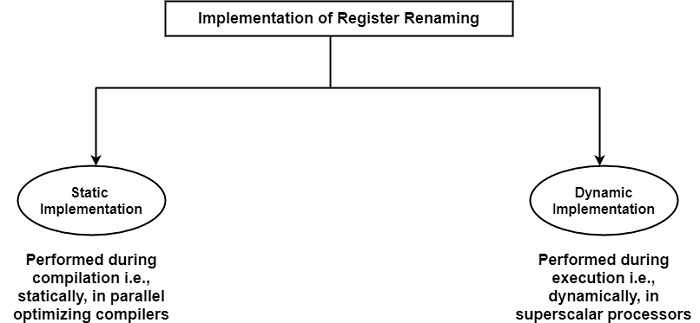

Register renaming can be implemented either statistically or dynamically as shown in the figure.

Static Implementation − In a static implementation, register renaming is carried out during compilation. This technique was first introduced in parallel optimizing compilers for pipelined processors, and later in superscalar processors.

Dynamic Implementation − When register renaming is implemented dynamically, renaming takes place during execution. This requires extra circuitry in terms of supplementary register space, additional data path, and logic. The dynamic renaming has been utilized in advanced superscalar processors because the early 1990s.

The renaming was introduced in two stages. In the first stage, the renaming was only partially implemented. Here, renaming is confined to one or a few particular data types. For instance, the Power1, Power2, PowerPC 601 and Nx586 processors employ partial renaming.

In both stages, IBM was the first vendor to introduce renaming, initially in its Power-line with the Power1 (RS/6000) and later in the high-end processors of its ES/9000 family. IBM continued to implement full renaming in the power-based PowerPC-line except for the first model, the PowerPC 601. All vendors of significant superscalar processors have introduced renaming in their most recent models, except DEC in its α-line and Sun in the UltraSparc.