Data Structure

Data Structure Networking

Networking RDBMS

RDBMS Operating System

Operating System Java

Java MS Excel

MS Excel iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C Programming

C Programming C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP

- Selected Reading

- UPSC IAS Exams Notes

- Developer's Best Practices

- Questions and Answers

- Effective Resume Writing

- HR Interview Questions

- Computer Glossary

- Who is Who

What is Dispatch policy?

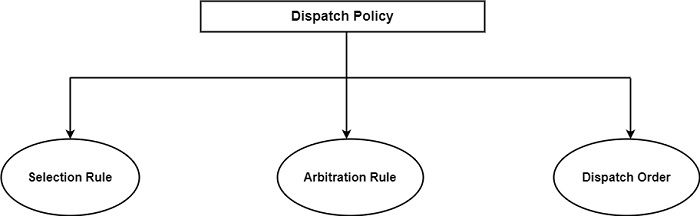

The dispatch policy specifies how instructions are selected for execution and how to dispatch blockages are handled. The dispatch policy can be considered as a scheduling policy consisting of the components specified as shown in the figure.

Selection Rule − The selection rule specifies when instructions are considered executable. Let us take it for granted that renaming is employed and unresolved conditional transfer instructions are managed by speculative branch processing.

Arbitration Rule − It can also need an arbitration rule for the case when more instructions are eligible for execution that can be disseminated in the next cycle. Most processors use a straightforward arbitration rule that prefers ‘older’ instruction over ‘younger’ ones. Power1, Power2, PowerPC 620, PM1 (Sparc64), and PentiumPro are examples that use this arbitration rule.

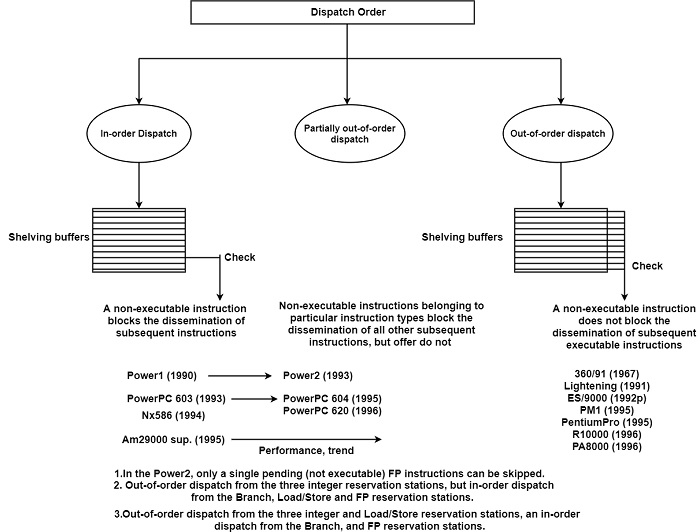

Dispatch Order − The dispatch order specifies whether a non-executable instruction avoids all consequent instructions from being dispatched as shown in the figure.

When an in-order dispatch scheme is employed, a non-executable instruction blocks any further dispatch. Thus, even if subsequent instructions were available for execution, they could not be dispatched. In-order dispatching impedes performance.

A slight performance increase may be achieved using a partially out-of-order dispatch. The Power2, PowerPC 604, and PowerPC 620 are processors using this approach. The Power2 shelves only FP instructions, and allows a single non-executable FP instruction to be skipped by an executable FP instruction during dispatching. The PowerPC 604 and PowerPC 620 dispatch instructions from particular reservation stations in order and other out-of-order.

Therefore, the PowerPC 604 performs in-order dispatch from the Branch, Load/Store, and FP reservation stations, whereas it dispatches instructions out-of-order from the three FX reservation stations.

The most advanced scheme is the out-of-order dispatch. Here, a non-executable instruction does not block the circulation of successive executable instruction. Instead, any executable instructions held in the shelving buffer are eligible for dispatch. From the implementation point of view, all or at least a large number of shelving buffer entries have to be inspected for executable instructions.

By contrast, in an in-order dispatch scheme, it suffices to check only the last buffer entry. A very early forerunner of out-of-order dispatch was the IBM 360/91 processor. The majority of most recent processors employ out-of-order dispatch.