Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

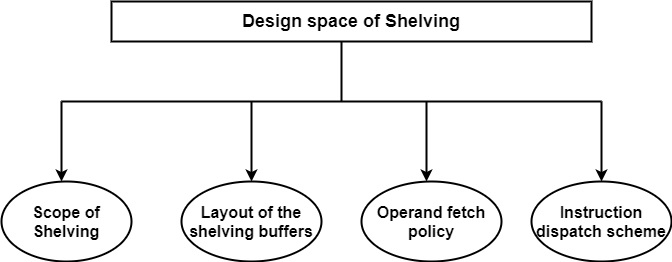

What is design space of shelving?

Shelving is an advanced issue mode, which is employed to eliminate issue blockages due to dependencies. Shelving makes use of dedicated instruction buffers, called shelving buffers, in front of each EU. The design space of shelving is shown in the figure. It consists of the following four main components such as the scope of shelving, the layout of shelving buffers used, the operand fetches policy and the instruction dispatch scheme.

Scope of Shelving

The scope of shelving specifies whether shelving is restricted to multiple instruction types or is performed for all instructions. Partial scheduling is only used in a few superscalar processors. Partial scheduling is an inadequate solution to the problem of removing issue blockages generated by dependencies. Full shelving covers all instruction types. Therefore most recent superscalar processors such as PowerPC 603, PowerPC 604, PentiumPro, etc.

Layout of the shelving buffers

Shelving buffers hold issued instructions just before they can be forwarded for execution to an EU. There are two types of shelving buffers, standalone shelving buffers and combiner buffers which are used for shelving, renaming, and reordering.

Shelving buffers are performed as standalone shelving buffers, that is, buffers that are used particularly for shelving. This type of shelving buffer is usually designated a reservation station.

The second approach is to use a mixed buffer for shelving, renaming, and reordering. In this case, the reorder buffer (ROB) which satisfies the coherent integrity of the program implementation, is continued such that it is used for shelving and register renaming.

Operand fetch policies

There are two types of operands fetch policies such as issue bound or dispatch bound. The issue-bound fetch policy defines that operands are fetched during instruction issues. In this method, shelving buffers influence instructions with their operand values, needing that the buffers be completely high to support the area for all the source operands.

The other basic operand fetch policy is the dispatch bound fetch policy, when operands are fetched during dispatching. In this case, shelving buffers contain short register identifiers instead of long operands.

The dispatch bound operand fetch policy has two benefits over the issue bound policy: the critical decode/issue path is smaller, and the shelving buffers are less complicated because register numbers needed significantly less buff area than operand values.

Instruction dispatch scheme

Instruction dispatch can be broken down into two basic tasks such as scheduling the instruction held in a particular reservation station for execution and disseminating the scheduled instruction or instruction for the allocated EU (s). The dispatch policy specifies how instructions are selected for execution and how to dispatch blockages are handled.

Many instructions can be dispatched from the shelving buffers in one cycle, termed the dispatch rate. The method for checking the availability of operands must also be specified. And finally, it must decide whether or not an empty reservation station may be bypassed.