- OS - Home

- OS - Overview

- OS - History

- OS - Evolution

- OS - Functions

- OS - Components

- OS - Structure

- OS - Architecture

- OS - Services

- OS - Properties

- Process Management

- Processes in Operating System

- States of a Process

- Process Schedulers

- Process Control Block

- Operations on Processes

- Process Suspension and Process Switching

- Process States and the Machine Cycle

- Inter Process Communication (IPC)

- Remote Procedure Call (RPC)

- Context Switching

- Threads

- Types of Threading

- Multi-threading

- System Calls

- Scheduling Algorithms

- Process Scheduling

- Types of Scheduling

- Scheduling Algorithms Overview

- FCFS Scheduling Algorithm

- SJF Scheduling Algorithm

- Round Robin Scheduling Algorithm

- HRRN Scheduling Algorithm

- Priority Scheduling Algorithm

- Multilevel Queue Scheduling

- Lottery Scheduling Algorithm

- Starvation and Aging

- Turn Around Time & Waiting Time

- Burst Time in SJF Scheduling

- Process Synchronization

- Process Synchronization

- Solutions For Process Synchronization

- Hardware-Based Solution

- Software-Based Solution

- Critical Section Problem

- Critical Section Synchronization

- Mutual Exclusion Synchronization

- Mutual Exclusion Using Interrupt Disabling

- Peterson's Algorithm

- Dekker's Algorithm

- Bakery Algorithm

- Semaphores

- Binary Semaphores

- Counting Semaphores

- Mutex

- Turn Variable

- Bounded Buffer Problem

- Reader Writer Locks

- Test and Set Lock

- Monitors

- Sleep and Wake

- Race Condition

- Classical Synchronization Problems

- Dining Philosophers Problem

- Producer Consumer Problem

- Sleeping Barber Problem

- Reader Writer Problem

- OS Deadlock

- Introduction to Deadlock

- Conditions for Deadlock

- Deadlock Handling

- Deadlock Prevention

- Deadlock Avoidance (Banker's Algorithm)

- Deadlock Detection and Recovery

- Deadlock Ignorance

- Resource Allocation Graph

- Livelock

- Memory Management

- Memory Management

- Logical and Physical Address

- Contiguous Memory Allocation

- Non-Contiguous Memory Allocation

- First Fit Algorithm

- Next Fit Algorithm

- Best Fit Algorithm

- Worst Fit Algorithm

- Buffering

- Fragmentation

- Compaction

- Virtual Memory

- Segmentation

- Paged Segmentation & Segmented Paging

- Buddy System

- Slab Allocation

- Overlays

- Free Space Management

- Locality of Reference

- Paging and Page Replacement

- Paging

- Demand Paging

- Page Table

- Page Replacement Algorithms

- Second Chance Page Replacement

- Optimal Page Replacement Algorithm

- Belady's Anomaly

- Thrashing

- Storage and File Management

- File Systems

- File Attributes

- Structures of Directory

- Linked Index Allocation

- Indexed Allocation

- Disk Scheduling Algorithms

- FCFS Disk Scheduling

- SSTF Disk Scheduling

- SCAN Disk Scheduling

- LOOK Disk Scheduling

- I/O Systems

- I/O Hardware

- I/O Software

- I/O Programmed

- I/O Interrupt-Initiated

- Direct Memory Access

- OS Types

- OS - Types

- OS - Batch Processing

- OS - Multiprogramming

- OS - Multitasking

- OS - Multiprocessing

- OS - Distributed

- OS - Real-Time

- OS - Single User

- OS - Monolithic

- OS - Embedded

- Popular Operating Systems

- OS - Hybrid

- OS - Zephyr

- OS - Nix

- OS - Linux

- OS - Blackberry

- OS - Garuda

- OS - Tails

- OS - Clustered

- OS - Haiku

- OS - AIX

- OS - Solus

- OS - Tizen

- OS - Bharat

- OS - Fire

- OS - Bliss

- OS - VxWorks

- Miscellaneous Topics

- OS - Security

- OS Questions Answers

- OS - Questions Answers

- OS Useful Resources

- OS - Quick Guide

- OS - Useful Resources

- OS - Discussion

Operating System - Paging

Paging is a memory management technique used by modern operating systems to manage the allocation of memory to processes. In this technique, the physical memory (i.e., the RAM) is divided into blocks of fixed size called frames, and the logical memory (i.e., the memory where the process is stored) is divided into blocks of the same size called pages. When a process is executed, its pages are loaded into available frames in the physical memory.

The image below shows working of paging in operating system −

Key Concepts Related to Paging

Here are some key concepts related to paging −

- Logical Address Space − The logical address space is the set of all logical addresses generated by a process in hard disk. It is divided into pages.

- Physical Address Space − The physical address space refers to the set of all physical addresses in the main memory (RAM). It is divided into frames.

- Page Table − A page table is a data structure used by the operating system to direct logical addresses to physical addresses. It stores information such as the location of each page in the physical memory.

- Page Number − The page number is the index of a page in the logical address space.

- Frame Number − The frame number is the index of a frame in the physical address space.

- Page Size − The page size is the size of each page and frame. It is usually represented as a power of 2, For example, 4KB, 8KB, etc.

Address Translation in Paging

When a process generates a logical address, the operating system uses the page table to translate it into a physical address. This process is known as address translation. The logical address is divided into two parts −

- The page number

- The offset within the page

The page number is used to search the corresponding frame number in the page table, and the offset is the location within that frame. The physical address is then calculated by combining the frame number and the offset. Here is the formula to calculate the physical address:

$$\mathrm{\text{Physical Address} \:=\: (\text{Frame Number } \:\times\: \text{ Page Size }) \:+\: \text{Offset}}$$

Page Table in Paging

The page table is a data structure inside the operating system that maps logical addresses and physical addresses. Each entry in the page table contains the following information:

- Frame Number − The frame number refer to the location of the page in physical memory.

- Valid/Invalid Bit − This bit is used to know if the page is in memory (valid) or not (invalid).

- Protection Bits − Bits that is used to indicate the permission of accessing the page (e.g., read, write, execute).

- Dirty Bit − A bit that is used to indicate if the page has been modified since it was loaded into memory.

- Reference Bit − A bit that is used to indicate whether the page has been accessed recently.

Example: Structure of a Page Table

Consider a system with following configuration −

- System A 32-bit system with a 4KB (212 bytes) page size.

- Logical Address Space 232 bytes (4GB).

- Physical Address Space 230 bytes (1GB).

- Number of Pages 232 / 212 = 220 pages.

In this case, the page table will have 220 entries. Each entry in the page table will contain the frame number, valid/invalid bit, protection bits, dirty bit, and reference bit. Consider that each entry takes 4 bytes, the total size of the page table will be −

$$\mathrm{\text{Size of Page Table} \:=\: \text{Number of Pages} \:\times\: \text{Size of Each Entry}}$$

$$\mathrm{=\: 2^{20} \:\times\: 4\: \text{ bytes} \:=\: 4 \text{ MB}}$$

Address Translation − Suppose a virtual address like 0 × 100000 is generated by a process. The page number can be calculated as:

$$\mathrm{\text{Page Number} \:=\: \frac{\text{Virtual Address}}{\text{Page Size}} \:=\: \frac{0 \:\times\: 100000}{0 \:\times\: 1000}}$$

$$\mathrm{=\: 0 \:\times\: 100}$$

The offset within the page can be calculated as −

$$\mathrm{\text{Offset} \:=\: \text{Virtual Address} \:\mod\: \text{Page Size}}$$

$$\mathrm{=\: 0 \times\: 100000 \mod\: 0 \:\times\: 1000 \:=\: 0 \:\times\: 000}$$

So, the virtual address 0x100000 refers to,

- Page Number: 0x100 (256 in decimal)

- Offset: 0x000 (0 in decimal)

The operating system will look up the page table entry for page number 0x100 to find the corresponding frame number. If the page is in memory (valid), it will get the frame number and calculate the physical address using the formula mentioned earlier.

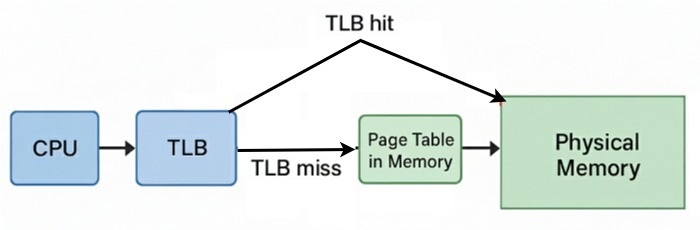

Translation Lookaside Buffer (TLB)

The Translation Lookaside Buffer (TLB) is a high speed cache inside CPU that stores recent values of translation made from virtual addresses to physical addresses. This will help to reduce the time taken for address translation, as it will store the most frequently used page table entries.

When a virtual address is generated, the TLB is checked first. If the entry is found in the TLB (a TLB hit occurs), the physical address can be obtained directly from the TLB. If the entry is not found in the TLB (a TLB miss occurs), the page table is used to get the frame number, and then the TLB is updated with this new entry.

Effective Access Time (EAT)

The Effective Access Time (EAT) is the average time taken to access a memory location, by considering both TLB hits and TLB misses. It can be calculated using the following formula −

$$\mathrm{\text{EAT} \:=\: (\text{H} \:\times\: \text{T}) \:+\: (\text{M} \:\times\: (\text{T} \:+\: \text{M.A.T}))}$$

Where,

- H = TLB Hit Ratio − The percentage of memory accesses that leads to TLB hit.

- M = TLB Miss Ratio − The percentage of memory accesses that leads to TLB miss (1 - TLB Hit Ratio).

- T = TLB Access Time − The time taken to access the TLB.

- M.A.T = Memory Access Time − The time taken to access the main memory.

For example, if the TLB hit ratio is 90%, TLB access time is 10 nanoseconds, and memory access time is 100 nanoseconds, the EAT can be calculated as follows −

$$\mathrm{\text{EAT} \:=\: (0.9 \:\times\: 10 \text{ ns}) \:+\: (0.1 \:\times\: (10 \text{ ns} \:+\: 100 \text{ ns}))}$$

$$\mathrm{=\: 9 \text{ ns} \:+\: 11 \text{ ns} \:=\: 20 \text{ ns}}$$

So, the effective access time in this case is 20 nanoseconds.

Pros and Cons of Paging

Here are some advantages of implementing paging in operating systems −

- Remove External Fragmentation − Paging helps to reduce external fragmentation issues by dividing memory into fixed-size pages and frames.

- Efficient Memory Utilization − By implementing paging, memory can be utilized more efficiently, because pages can be loaded into any available frame in physical memory.

- Simplified Memory Management − Paging simplifies management of memory inside the operating system. It eliminates the need for contiguous allocation of memory.

- Extra Physical Memory − Paging allows the use of secondary storage (like hard disk) as an extension of physical memory, which is known as virtual memory.

Paging comes with some disadvantages as well, such as −

- Overhead of Page Table − If the size of the page table is large, it will consume large amount of memory and can lead to performance issues.

- Increased Memory Access Time − During address translation, if there is a TLB miss, then it will take more time to access the page table, which can increase the overall memory access time.

- Extra Complexity − Implementing paging adds extra complexity while creating operating system.

Conclusion

We have learned that paging is a memory management technique used in modern operating systems. It enhances memory utilization by mapping logical addresses to physical addresses using a page table. The page table stores information about each page, such as frame number, reference bit, etc.

Even though paging is a modern memory management technique, it has some disadvantages like creating overhead of page table and increased memory access time. However, still paging is commonly used in operating systems for efficient memory management.