Data Structure

Data Structure Networking

Networking RDBMS

RDBMS Operating System

Operating System Java

Java MS Excel

MS Excel iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C Programming

C Programming C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP

- Selected Reading

- UPSC IAS Exams Notes

- Developer's Best Practices

- Questions and Answers

- Effective Resume Writing

- HR Interview Questions

- Computer Glossary

- Who is Who

Memory speed requirement in 8085 Microprocessor

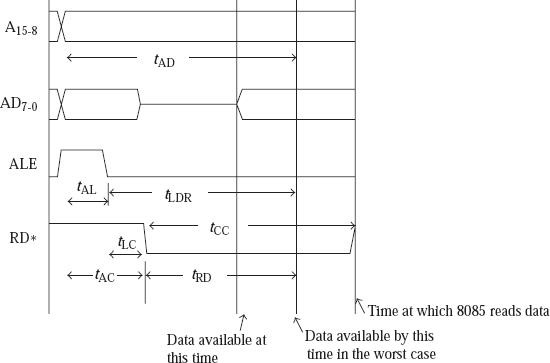

At the end of the state T2 in a machine cycle, 8085 processor senses the Ready input pin. If it is logic 0, 8085 processors enter the Twait state, else it enters to the T3 state. The Ready input is permanently fixed to logic 1. The memory chips and the Input Output ports in the system same speed with 8085. Else appropriate number of wait states should be generated by the external circuit. In fact, in the ALS kit the Ready pin should be fixed to logic 1

As an example, we check up if the 27128A-20 16K×8 EPROM chip are used without any wait states with a 8085 processor which operates at 320 nS clock period. So for interfacing a memory chip, the most important timing parameters are tcc, tCE, and tOE.

For 27128A-20 chip, the characteristics are as follows.

tAcc is equal to 200 nS max

tCE is equal to 200 nS max

tOE is equal to 75 nS max

Maximum time of 200 nS is needed for the data output after stable address is received by the 27128, under the following assumptions.

The memory chip should be selected at least 200 nS (tCE) before the data gets output through it.

The output enable line of the memory chip should have been activated for at least 75 nS (tOE) before we output the data.