Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Selected Reading

Earliest data output time considering TACC in 8085 Microprocessor

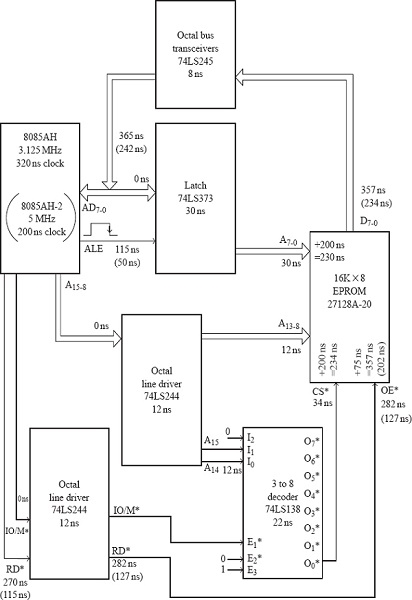

27128 receives the Address A13-8 by 27128 from 8085AH by means of the octal line driver 74LS244, which has a propagation delay of 12 nS. Address ranging from A7-0 is received by 27128 from 8085AH by means of 74LS373 octal latch, which consists of a propagation delay of 30 nS. Thus, address ranging from A13-0 is received by 27128 at the end of 30 nS. So the data only comes out on D7-0 pins of 27128 by 30 nS + tAcc = 30 nS + 200 nS = 230 nS.

Delays involved in accessing 27128 EPROM in ALS kit.

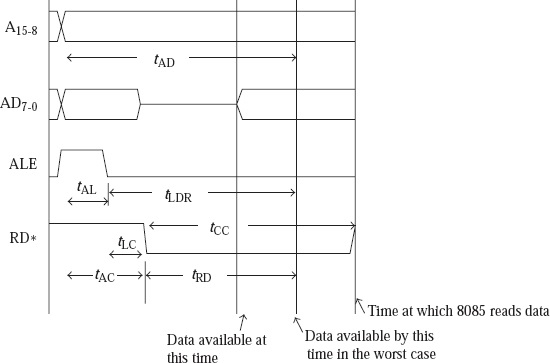

Bus timing characteristics of MR machine cycle

Advertisements