- Microprocessor - Home

- Microprocessor Overview

- Microprocessor Classification

- Microprocessor Evolution

- Microprocessor Components

- Microprocessor Characteristics

- Microprocessor Functions

- Microprocessor Pros & Cons

- Microprocessor Application

- Microcontrollers Types

- Microcontrollers Pros & Cons

- 8085 Microprocessor Architecture

- 8085 Microprocessor Pin Configuration

- Addressing Modes & Interrupts

- 8085 Microprocessor Instruction Sets

- 8085 Microprocessor Features

- Externally Initiated Operations

- 8086 Microprocessor

- 8086 Microprocessor Overview

- Functional Units

- Pin Configuration

- Instruction Sets

- 8086 Microprocessor Interrupts

- 8086 Microprocessor Addressing Modes

- 8086 Microprocessor Features

- Memory Segmentation

- Auxiliary Carry Flag

- Maximum and Minimum Mode Configurations

- Multiprocessor Configuration

- Configuration Overview

- 8087 Numeric Data Processor

- I/O Interfacing

- I/O Interfacing Overview

- 8279 Programmable Keyboard

- 8257 DMA Controller

- Serial vs Parallel Communication

- Serial Communications Interface

- Parallel Communication Interface

- 8051 Microcontrollers

- Microcontrollers Overview

- 8051 Microcontrollers Architecture

- 8051 Pin Description

- 8051 Input Output Ports

- 8051 Microcontrollers Interrupts

- Instruction Sets

- Logical Instructions in AVR

- Conditional Branch Instructions AVR

- Arithmetic Instructions in AVR

- External Memory Interfacing

- Time Delay in AVR

- 8051 vs PIC Microcontroller

- Peripheral Devices

- Peripheral Devices

- Programmable Peripheral Interface

- Intel 8255A Pin Description

- Programmable Interval Timer

- 8253/54 Operational Modes

- Interfacing Devices

- Applications and Furture Trends

- Microcontrollers - Application

- Microprocessors and Microcontrollers in IoT

- Microcontrollers in Automotive Systems

- Microcontrollers - Low-Power

- Artificial Intelligence Processors

- Microprocessor Useful Resources

- Microprocessor - Quick Guide

- Microprocessor - Useful Resources

- Microprocessor - Discussion

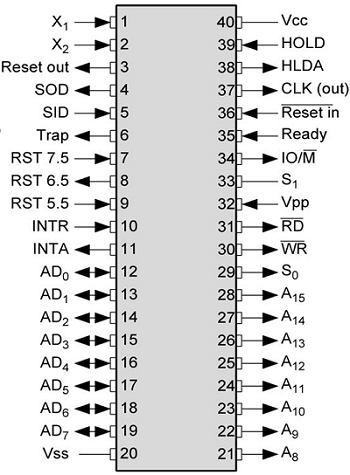

Microprocessor - 8085 Pin Configuration

The following image depicts the pin diagram of 8085 Microprocessor −

The pins of a 8085 microprocessor can be classified into seven groups −

Address bus

A15-A8, it carries the most significant 8-bits of memory/IO address.

Data bus

AD7-AD0, it carries the least significant 8-bit address and data bus.

Control and status signals

These signals are used to identify the nature of operation. There are 3 control signal and 3 status signals.

Three control signals are RD, WR & ALE.

RD − This signal indicates that the selected IO or memory device is to be read and is ready for accepting data available on the data bus.

WR − This signal indicates that the data on the data bus is to be written into a selected memory or IO location.

ALE − It is a positive going pulse generated when a new operation is started by the microprocessor. When the pulse goes high, it indicates address. When the pulse goes down it indicates data.

Three status signals are IO/M, S0 & S1.

IO/M

This signal is used to differentiate between IO and Memory operations, i.e. when it is high indicates IO operation and when it is low then it indicates memory operation.

S1 & S0

These signals are used to identify the type of current operation.

Power supply

There are 2 power supply signals − VCC & VSS. VCC indicates +5v power supply and VSS indicates ground signal.

Clock signals

There are 3 clock signals, i.e. X1, X2, CLK OUT.

X1, X2 − A crystal (RC, LC N/W) is connected at these two pins and is used to set frequency of the internal clock generator. This frequency is internally divided by 2.

CLK OUT − This signal is used as the system clock for devices connected with the microprocessor.

Interrupts & externally initiated signals

Interrupts are the signals generated by external devices to request the microprocessor to perform a task. There are 5 interrupt signals, i.e. TRAP, RST 7.5, RST 6.5, RST 5.5, and INTR. We will discuss interrupts in detail in interrupts section.

INTA − It is an interrupt acknowledgment signal.

RESET IN − This signal is used to reset the microprocessor by setting the program counter to zero.

RESET OUT − This signal is used to reset all the connected devices when the microprocessor is reset.

READY − This signal indicates that the device is ready to send or receive data. If READY is low, then the CPU has to wait for READY to go high.

HOLD − This signal indicates that another master is requesting the use of the address and data buses.

HLDA (HOLD Acknowledge) − It indicates that the CPU has received the HOLD request and it will relinquish the bus in the next clock cycle. HLDA is set to low after the HOLD signal is removed.

Serial I/O signals

There are 2 serial signals, i.e. SID and SOD and these signals are used for serial communication.

SOD (Serial output data line) − The output SOD is set/reset as specified by the SIM instruction.

SID (Serial input data line) − The data on this line is loaded into accumulator whenever a RIM instruction is executed.