Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

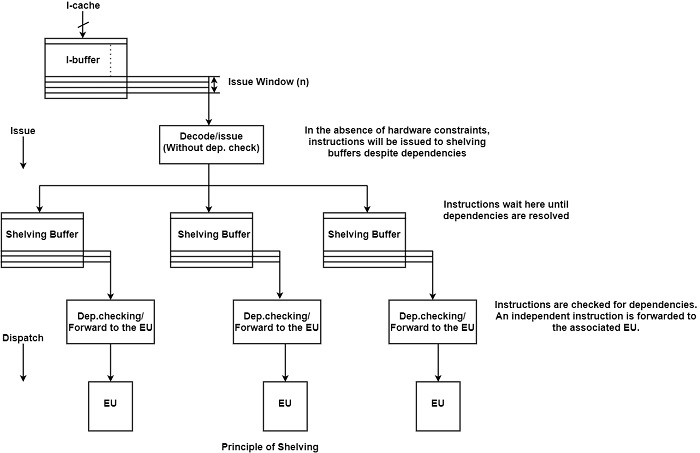

What is Shelving?

Shelving is an advanced issue mode, which is employed to eliminate issue blockages due to dependencies. Shelving makes use of dedicated instruction buffers, called shelving buffers, in front of each EU. Shelving decouples dependency checking from the instruction issue, and defers to it the dispatch phase.

It can more precisely with shelving decoded instructions are used to shelving buffers despite data or control dependencies or busy EUs. This removes the issue bottleneck of the blocking issue.

Specific resource constraints can restrict the processor to issue fewer instructions in a cycle than its issue rate. There are two resource constraints such as the lack of free entries in the targeted shelving buffer, in the rename register file, or the ROB. The data path restrictions and limiting the number of instructions that can be transferred in one cycle to the allocated shelving buffer. In the case of an issue blockage, processors with shelving usually employ in-order, aligned-issue, etc.

Instructions are held in the shelving buffers until dependencies are resolved and instructions can be forwarded to the EUs. When an EU becomes free, the associated shelving buffers are checked for instructions eligible for execution. An instruction not bound to any dependency is eligible for execution. One of the eligible instructions is selected for execution according to the dispatch policy used and will be forwarded to the connected EU.

The processors which use shelving predominantly employ the advanced superscalar issue policy. This represents that shelving is generally employed in connection with speculative execution of unresolved control dependency and register renaming.

Speculative branch processing eliminates execution blockages because of unresolved control dependencies while renaming eliminates issue blockages because of false register data dependencies that are, because of WAR and WAW dependencies.

Then only true data dependencies can avoid instructions held in the shelving buffers from execution. Consequently, during instruction dispatch, dependency checking is reduced to check for true data dependencies (RAW dependencies).

This is exactly the dataflow principle of operation. Therefore a superscalar processor with shelving, speculative branch processing, and register renaming executes instructions on the dataflow basis. It concerns the preservation of sequential consistency, which calls for maintaining the logical integrity of the execution even though instructions are executed in parallel.

Shelving creates processing more distributed because the dispatch window is much broad than the issue window. Therefore, shelving is frequently used together with an advanced approach of retaining sequential consistency known as instruction reordering.