Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instruction type XCHG in 8085 Microprocessor

In 8085 Instruction set, there is one mnemonic XCHG, which stands for eXCHanGe. This is an instruction to exchange contents of HL register pair with DE register pair. This instruction uses implied addressing mode. As it is1-Byte instruction, so It occupies only 1-Byte in the memory. After execution of this instruction, the content between H and D registers and L and E registers will get swapped respectively.

| Mnemonics, Operand | Opcode(in HEX) | Bytes |

|---|---|---|

| XCHG | EB | 1 |

Let us suppose, HL and DE register pairs are having ABCDH and 6789H contents respectively. After execution of instruction XCHG the contents of HL and DS register pairs will be 6789H and ABCDH respectively. Here is the content training table for the better understanding.

| Before | After | |

|---|---|---|

| (HL) | ABCDH | 6789H |

| (DE) | 6789H | ABCDH |

| Address | Hex Codes | Mnemonic | Comment |

|---|---|---|---|

| 2006 | EB | XCHG | Swapping the contents of DE and HL register pairs |

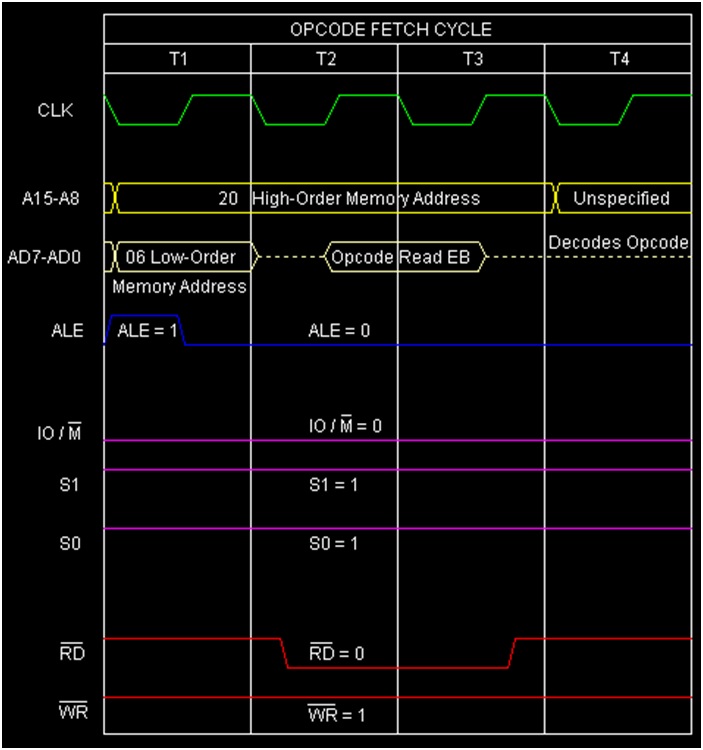

Let us see the timing diagram of this instruction XCHG as below −

Summary − So this instruction XCHG requires 1-Byte, 4-Machine Cycles (Opcode Fetch) and 4 T-States for execution as shown in the timing diagram.