Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instruction type NOP in 8085 Microprocessor

In 8085 Instruction set, NOP is an instruction which is falling under Machine Control Instruction category. NOP is a mnemonic that stands for "No Operation". This instruction does nothing during execution. Only it occupied 1-Byte of memory space and spends 4-Machine Cycles.

| Mnemonics, Operand | Opcode(in HEX) | Bytes |

|---|---|---|

| NOP | 00 | 1 |

In spite of the fact that it does nothing, still it has got many different applications. It is useful in the following cases −

NOP instruction can be used to create small-time delay in the execution of the code. It is very useful for generating small-time delays of the order of a few microseconds.

8085 Microprocessor works faster compared to the speed of its other peripheral devices. So introduction of this NOP instruction can produce synchronization of the speed between these two.

NOP instruction is very useful when we require to keep some memory space void with in our program for future instruction insertions accordingly. In future when extra code is to be inserted then we can replace NOP instructions and can do needful accordingly.

Thus, it is a good programming practice to have a few NOP instructions in the program at regular intervals od code, especially during program development. Otherwise "Insert" and "Delete" keys are available on our microprocessor kit, which might help us for new code insertion and pre-existing code deletion.

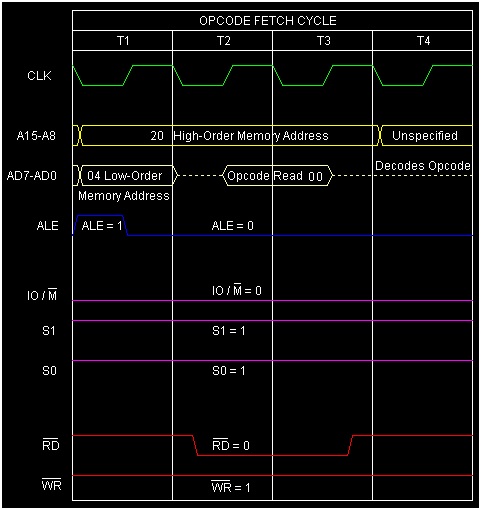

The timing diagram against this instruction NOP execution is as follows −

Summary − So this instruction NOP requires 1-Byte, 1-Machine Cycle (Opcode Fetch) and 4 T-States for execution as shown in the timing diagram.