Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

Instruction type LHLD a16 in 8085 Microprocessor

In 8085 Instruction set LHLD is a mnemonic that stands for Load HL pair using Direct addressing from memory location whose 16-bit address is denoted as a16. So the previous content of HL register pair will get updated with the new 16-bits value. As HL pair has to be updated, so data comes from two consecutive memory locations starting at the address a16 and also from next address location. This instruction uses absolute addressing mode for specifying the data in the instruction. It occupies 3-Bytes in the memory.

| Mnemonics, Operand | Opcode(in HEX) | Bytes |

|---|---|---|

| LHLD Address | 2A | 3 |

Let us consider one example instruction LHLD 4050H falling in this category. This instruction will occupy 3-Bytes and so 3 memory locations. First Byte will contain opcode 2AH, second Byte will contain the low order address Byte 50H and last Byte will contain high order address Byte 40H. Let us suppose, 4050H and 4051H memory locations are holding values AAH and BBH respectively. Also HL register pair is containing initial value like CCH and DDH. Now after execution of LHLD 4050H instruction, the updated content of HL register pair will become AABBH. Let us consider the following tracing table for better understanding.

| Before | After | |

|---|---|---|

| (4050H) | BBH | BBH |

| (4051H) | AAH | AAH |

| (H) | CCH | AAH |

| (L) | DDH | BBH |

| Address | Hex Codes | Mnemonic | Comment |

|---|---|---|---|

| 200B | 2A | LHLD 4050H | Initialize HL register pair from 4050H and 4051H memory locations? contents. |

| 200C | 50 | Low order Byte of the address | |

| 200D | 40 | High order Byte of the address |

Note that there are no instructions in 8085 like LBCD a16 and LDED a16. As HL pair is the most important register pair, whose contents can be loaded in more ways than any other register pair.

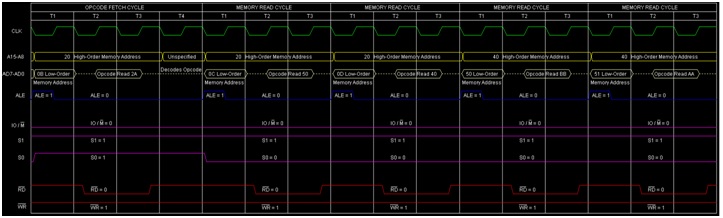

Let us now consider the timing diagram of this instruction LHLD 4050H below.

Summary − So this instruction LHLD 4050H requires 3-Bytes, 5-Machine Cycles (Opcode Fetch, Memory Read, Memory Read, Memory Read, Memory Read) and 16 T-States for execution as shown in the timing diagram.