Article Categories

- All Categories

-

Data Structure

Data Structure

-

Networking

Networking

-

RDBMS

RDBMS

-

Operating System

Operating System

-

Java

Java

-

MS Excel

MS Excel

-

iOS

iOS

-

HTML

HTML

-

CSS

CSS

-

Android

Android

-

Python

Python

-

C Programming

C Programming

-

C++

C++

-

C#

C#

-

MongoDB

MongoDB

-

MySQL

MySQL

-

Javascript

Javascript

-

PHP

PHP

-

Economics & Finance

Economics & Finance

RST7.5 pin in 8085

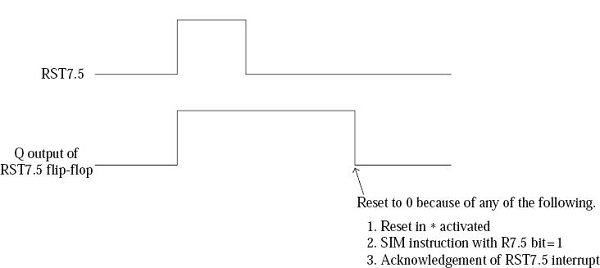

RST7.5 pin is an input which is edge-sensitive. Peripherals uses it for sending a pulse, rather than a sustained high level, for the interruption of the processor. Internal to 8085 we have a flip-flop which gets connected to the interrupt pin RST7.5. We set this flip-flop to 1, when a positive-going edge occurs on the input RST 7.5. The waveform of pin RST7.5 and output Q of RST7.5 flip-flop is shown in the Fig.

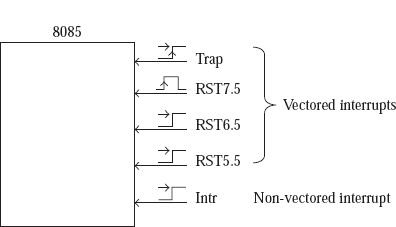

Internal interrupt signal RST7.5 has a priority higher than the internal interrupt signals of RST6.5, RST5.5 and INTR. As we can see from fig the RST7.5 internal interrupt signal is activated only when

At logic 1 the output Q of the RST7.5 flip-flop;

Flip-Flop IE is in logic 1 state;

-

RST7.5 interrupt is not masked by SIM instruction.